4 半整數分頻器設計

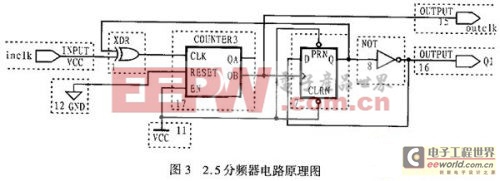

現通過設計一個分頻系數為2.5的分頻器給出用FPGA設計半整數分頻器的一般方法。該2.5分頻器由模3計數器、異或門和D觸發器組成。

圖3 2.5分頻器電路原理圖

4.1 模3計數器

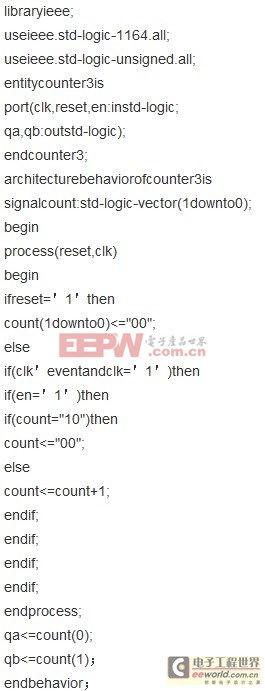

該計數器可產生一個分頻系數為3的分頻器,并產生一個默認的邏輯符號COUNTER3。其輸入端口為RESET、EN和CLK;輸出端口為QA和QB。下面給出模3計數器VHDL描述代碼:

任意模數的計數器與模3計數器的描述結構完全相同,所不同的僅僅是計數器的狀態數。上面的程序經編譯、時序模擬后,在MAX+PLUSII可得到如圖2所示的仿真波形。

分頻器相關文章:分頻器原理

評論