基于FPGA的USB接口數據采集系統設計

摘 要:介紹了一種高速實時數據采集系統的設計。該系統以FPGA作為邏輯控制的核心,以USB2.0作為與上位機數據傳輸的接口,能同時支持單端16路和差分8路模擬信號輸入,最大采樣率為200 kHz,12位的轉換精度。描述了系統的主要組成和FPGA模塊化設計的實現方法,并給出了其核心模塊的時序仿真波形圖。

關鍵詞: FPGA; USB2.0; 數據采集; 轉換精度

傳統的數據采集系統中通常采用單片機或DSP作為控制模塊,控制A/D轉換、存儲和其他外圍電路的工作,利用PCI、ISA等接口與上位機進行通信。隨著數據采集對速度、實時性、簡易性的要求越來越高,傳統數據采集系統的弊端也日趨明顯。近年來隨著FPGA技術和USB技術的應用深度和廣度的不斷加大,利用FPGA芯片和USB接口設計高速數據采集系統成為新的研究熱點。FPGA芯片不僅體積小、功耗低、時鐘頻率高、內部時延小,而且能夠使用VHDL語言來編程實現程序的并行執行,配置靈活,開發周期短,性能可靠。USB是一種高效、快速、價格低廉、體積小并支持熱插拔的新型串行通信接口,目前USB2.0的高速傳輸速率能夠達到480 Mb/s,能夠實現數據的高速傳輸。

1 系統總體結構

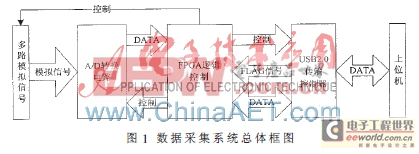

本設計采用FPGA+USB的設計思路,利用FPGA芯片作為系統的邏輯控制核心,通過USB 2.0接口與上位機通信,實現單端16路/差分8路模擬數據的高速、實時、便攜式的采集。本文設計的數據采集系統劃分為A/D轉換電路、FPGA采集控制和USB傳輸控制器等若干部分。如圖1所示。

本數據采集系統支持單端16路和差分8路模擬信號輸入,每路12 bit的轉換精度,最高采樣率為200 kHz。主機應用程序首先向USB控制器發出采樣時控包,在時控包中設置采集通道及其采樣頻率。進而USB控制器觸發FPGA采集信息,FPGA根據時控包開始啟動A/D進行模數轉換,轉換結束后,FPGA接受A/D輸出的12 bit串行數據,并通過串并轉換將它轉換成16 bit并行數據輸出。然后將采集到的數據信息通過USB控制器發送給主機,最后由主機做進一步信息處理。

2 主要芯片選型

本數據采集系統用到的主要芯片包括FPGA芯片、A/D轉換芯片和USB傳輸控制芯片。

2.1 FPGA芯片的選取

依據本系統設計的需要選用Altera公司的Cyclone II系列EP2C8Q208C8。該芯片內部邏輯單元8 256個,有165 888個RAM位,182個可用I/O口,系統時鐘頻率高于260 MHz,只需要3.3 V和1.2 V的工作電壓,完全能夠滿足設計的要求。

2.2 ADC轉換芯片的選取

考慮到系統的采樣率、分辨率、通道數等要求,本系統選用德州儀器公司(TI)的ADS7817模數轉換器。該器件是12位的低功耗、高阻抗全差分模擬輸入、具有串行輸出接口的模數轉換器,內部基準電壓范圍為100 mV~2.5 V,最高采樣率200 kHz,相應輸入分辨率范圍49 μV~1.22 mV。

2.3 USB傳輸控制芯片的選取[1]

本系統選用CYPRESS公司的USB2.0外設控制器EZ-USB FX2 CY7C68013-56。該芯片包括帶8.5 KB片上RAM的高速8051單片機、4 KB FIFO存儲器以及通用可編程接口(GPIF)、串行接口引擎(SIE)和USB2.0收發器,可與任何ASIC或DSP進行接合,并且還支持所有通用總線標準,性價比較高。USB2.0協議提供480 Mb/s的傳輸速度,因此CY7C68013是USB2.0的完整解決方案。

3 系統硬件設計方案實現

3.1 FPGA與ADC及模擬多路開關的電路設計

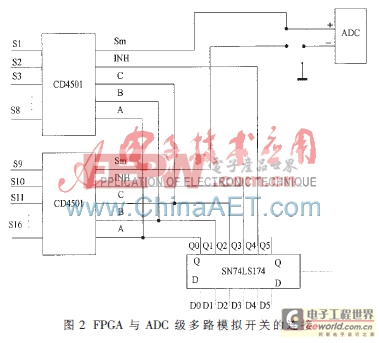

系統選用8通道模擬多路開關CD4501和SN74LS174集成D觸發器組合構成FPGA信號采集控制的輸入通道。本系統要求支持單端16路和差分8路模擬信號輸入,因此使用2片CD4501來實現最大16路模擬輸入通道的多路復用。在選擇單端或差分輸入時,通過硬件開關來實現。在一個采樣周期內,選擇哪路模擬信號進行A/D轉換由FPGA控制D觸發器SN74LS174其中的5個D輸入端的電平高低來選擇通道實現。每路模擬信號都要經過多路模擬開關選擇通道后,再送入A/D芯片的輸入端,如圖2所示。本方案中,FPGA為采樣通道SN74LS174提供30 MHz的時鐘CLK1及復位信號CLR,為A/D芯片提供3 MHz的同步時鐘信號DCLK和片選信號CS,從而使A/D芯片對相應的通道進行數據轉換。

評論