在FPGA上建立一個UWB脈沖發生器

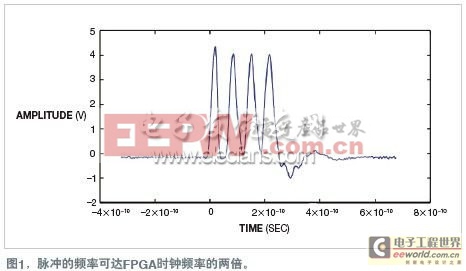

用大多數FPGA都可以實現一個數字UWB(超寬帶)脈沖發生器。本設計可以創建一個兩倍于FPGA時鐘頻率的脈沖信號(圖1)。以前的設計要采用異步延遲,才能制造出所需頻率的脈沖。不過該設計需要一只支持三態上拉的FPGA,如Xilinx公司的Virtex 2(參考文獻1)。這種方案亦需要手工布局與布線。今天的FPGA都不支持三態上拉。另外,異步延遲會隨溫度而變化。本例采用了一種有多時鐘相位組合的同步延遲方案。這一設計可以實現于所有類別的FPGA上。

本設計中的主要限制因素是DCM(數字時鐘管理器)以及觸發器的主時鐘頻率。例如,Xilinx公司Virtex 4的DCM不能超過400 MHz。一片FPGA可以生成頻率為時鐘頻率一半的信號,因為它用兩個時鐘脈沖使信號從0轉換為1,再回到0。因此,不能直接生成大于時鐘頻率一半的頻率。本設計用DCM的多時鐘相位以及小于單個時鐘周期的同步延遲,可以產生出高于時鐘頻率一半的脈沖信號,達到時鐘頻率的兩倍。

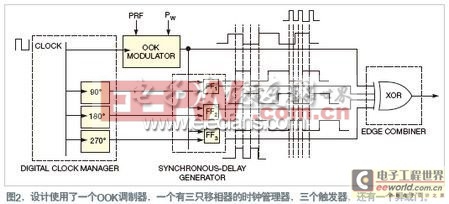

圖2即所稱的脈沖發生器。它包括三個功能塊:一個OOK(on/off鍵控)調制器、一個同步延遲發生器,還有一個包含一只異或門的邊沿結合器。OOK調制器由一只反相器構成,它在每個新脈沖的開始時作為脈沖重復頻率信號觸發器。當發生一個觸發時,OOK電路將一個預初始化的信號轉換成為一個時間,該時間等于來自一個脈沖帶寬的計數值,然后在下個觸發出現前保持為零。OOK塊產生的頻率是時鐘頻率的一半。這個OOK輸出通過同步延遲發生器,產生出三個延遲版的OOK輸出。

這些延遲都小于一個時鐘周期。時鐘相位依次為觸發器FF1、FF2和FF3提供時鐘,它們分別延遲90°、180°和 270°。這些延遲脈沖再使用組合邏輯,與OOK調幅器的輸出相結合,產生出UWB脈沖所需要的頻率。邊沿結合器完成一次XOR(異或)運算,獲得的信號頻率取決于希望組合的邊沿。將OOK輸出邊沿與FF1 輸出相結合,就得到一個等于時鐘頻率的信號。將所有輸出邊沿結合起來,就得到一個兩倍于時鐘頻率的信號。DCM對這些延遲做同步,產生一個精確的信號頻率。本設計的復雜性小于參考文獻1中的異步延遲方案。

評論