一種基于音頻解嵌的異步FIFO設(shè)計(jì)及FPGA實(shí)現(xiàn)

在視音頻嵌入解嵌系統(tǒng)中,嵌入音頻、音頻解嵌與音頻轉(zhuǎn)換成音頻幀標(biāo)準(zhǔn)格式輸出都是工作在不同的時鐘頻率下的。多時鐘帶來的問題就是如何設(shè)計(jì)異步時鐘之間的接口電路。

異步FIFO存儲器是一種在數(shù)據(jù)交互系統(tǒng)中得到廣泛應(yīng)用的先進(jìn)先出邏輯器件,具有容納異步信號的頻率(或相位差異)的特點(diǎn)。使用異步FIFO可以在兩個不同時鐘系統(tǒng)之間快速而方便地傳輸實(shí)時數(shù)據(jù)。因此,異步FIFO被廣泛應(yīng)用于實(shí)時數(shù)據(jù)傳輸、網(wǎng)絡(luò)接口、圖像處理等方面。

雖然目前也出現(xiàn)了一些通用的異步FIFO內(nèi)核,但在一些具體環(huán)境下其工作效率并不是最理想的。針對這個問題,本文介紹了一種適合音頻解嵌的高效異步FIFO,對通用異步FIFO進(jìn)行了一些改進(jìn),最后利用Verilog HDL硬件描述語言設(shè)計(jì)并仿真實(shí)現(xiàn)。

1 SDI音頻嵌入基本格式

在模擬視頻中存在著行、場消隱期,而行、場消隱期內(nèi)并不存在有效圖像信號。對于數(shù)字視頻信號,同樣地也存在沒有有效視頻信號的區(qū)間。

模擬視頻中的行消隱期間,在數(shù)字視頻中被稱為行輔助數(shù)據(jù)區(qū)HANC(Horizontal Ancillary Data)。分量數(shù)字視頻格式的每一個有效行中,625/50制共有1 728個取樣字(525/60制為1 716個取樣字),其中對Y、Cb和Cr取樣有1 440個取樣字(0~1 439)。而對行消隱期間的取樣可以有288個取樣字(525/60制為276個取樣字)。

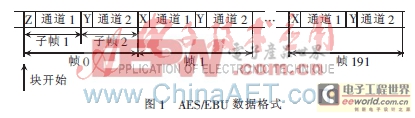

目前輔助數(shù)據(jù)區(qū)也即行消隱區(qū)最大的用途是放置數(shù)字音頻,被放置的數(shù)字音頻稱為嵌入音頻。圖1是AES/EBU音頻數(shù)據(jù)塊結(jié)構(gòu)[1]。

一個音頻塊由192個連續(xù)幀組成,每個幀包含相關(guān)的兩個子幀,使得一個數(shù)字音頻碼流可以作為立體聲、雙聲道模式使用。這兩個子幀(32 bit)分別表示一個音頻通道中的一個音頻樣本,每個子幀的32 bit中包含24 bit的音頻數(shù)據(jù)和一些輔助數(shù)據(jù)。

音頻嵌入就是將每個子幀的32 bit信息按照SMPTE-292[2]標(biāo)準(zhǔn)分別嵌入到3個數(shù)據(jù)字和一個輔助數(shù)據(jù)字中,并將這些數(shù)據(jù)字嵌入到HANC中。解嵌的目的就是把每個音頻子幀對應(yīng)的這4個字找到,按照順序把這些子幀組合成AES/EBU音頻塊格式,使輸出為直接可識別的音頻碼流。

2 通用異步FIFO設(shè)計(jì)

2.1 通用異步FIFO結(jié)構(gòu)

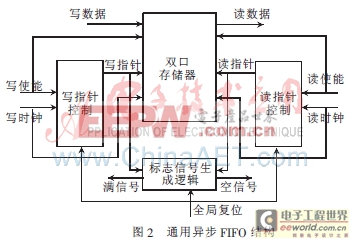

圖2所示為通用異步FIFO結(jié)構(gòu),一般由四個模塊構(gòu)成:數(shù)據(jù)存儲模塊、寫地址產(chǎn)生模塊、讀地址產(chǎn)生模塊和標(biāo)志位產(chǎn)生模塊。

系統(tǒng)分為讀時鐘和寫時兩個完全獨(dú)立的時鐘域。讀寫兩端的使能和時鐘信號作為讀寫指針控制的基礎(chǔ)控制輸入信號。更新的讀寫指針既作為存儲器的寫入讀出地址又作為標(biāo)志信號模塊的輸入。標(biāo)志產(chǎn)生模塊通過對讀寫地址的比較來得到存儲器的空、滿標(biāo)志信號。將寫滿信號和讀空信號分別反饋到寫指針和讀指針控制模塊,控制指針值的更新。

2.2 亞穩(wěn)態(tài)消除方法

由于讀寫標(biāo)志控制分別工作于不同的時鐘域,在其產(chǎn)生電路中,如果比較觸發(fā)器建立時間和保持時間的要求沒有得到滿足,觸發(fā)器就會進(jìn)入一個介于邏輯1和邏輯0的中間狀態(tài),稱之為亞穩(wěn)態(tài)。為了降低亞穩(wěn)態(tài)發(fā)生的概率,可采用格雷碼地址計(jì)數(shù)[3]。二進(jìn)制計(jì)數(shù)器在計(jì)數(shù)值增加時,可能同時會有多位數(shù)值發(fā)生變化,而格雷碼計(jì)數(shù)器每次加1只有一位數(shù)值發(fā)生變化。所以將二進(jìn)制讀寫指針轉(zhuǎn)換為格雷碼,送到另一個時鐘域進(jìn)行比較,可以降低亞穩(wěn)態(tài)發(fā)生的概率。

2.3 空、滿標(biāo)志產(chǎn)生

通過對讀寫格雷碼地址高兩位的比較,得到存儲器工作的滿空趨勢[4],再比較地址值是否相等最終判斷空、滿標(biāo)志。把這兩個2 bit數(shù)組合成4 bit數(shù)的16種組合,可以得到:當(dāng)寫地址格雷碼最高兩位和讀地址格雷碼最高兩位分別組合為:0001、0111、1110、1000時,存儲器趨向滿狀態(tài);為0100、1101、1011、0010時,存儲器趨向空狀態(tài)。

空、滿趨勢通過事件觸發(fā),隨時根據(jù)讀寫地址的更新值進(jìn)行判斷。再結(jié)合讀寫地址的比較結(jié)果來最終判斷存儲器的空、滿狀態(tài)。

3 改進(jìn)型異步FIFO設(shè)計(jì)

3.1 改進(jìn)方案

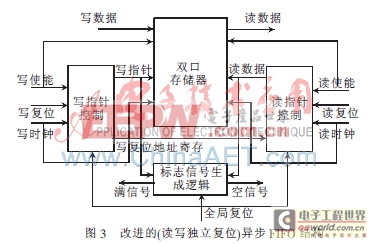

根據(jù)AES/EBU音頻格式可知,每192幀(384子幀)音頻構(gòu)成一個AES/EBU音頻塊,作為一個連續(xù)輸出單位,并用一個Z標(biāo)志來指示這一音頻塊的開始。根據(jù)這一標(biāo)準(zhǔn),本文設(shè)計(jì)了一種專用于該音頻格式輸出的異步FIFO。該異步FIFO具有單端復(fù)位,并根據(jù)寫地址復(fù)位寄存值作為讀地址更新的參考,使讀數(shù)據(jù)更可靠。FIFO深度設(shè)計(jì)為384子幀,位寬為24 bit。當(dāng)用每個存儲單元(24 bit)存儲一個子幀中的音頻數(shù)據(jù)碼來指示地址時,由于設(shè)計(jì)深度為384子幀,利用9 bit格雷碼來指示地址時,最高兩位不會達(dá)到10的情況下,那么在滿、空標(biāo)志判斷中的趨勢判斷就可以少考慮一種情況,即寫、讀地址格雷碼最高兩位組合為0001、0111、1100時,趨向滿;為0100、1101、0011時,趨向空。這種改善,既減小了存儲器的大小,又減小了程序的復(fù)雜度。

考慮到解嵌的音頻信號可能存在丟幀、錯幀,有的時候可能一塊數(shù)據(jù)中并沒有192幀的數(shù)據(jù),而只是一部分?jǐn)?shù)據(jù),因此,在實(shí)際工作中需要利用塊開始標(biāo)志Z復(fù)位寫地址指針。為了保證輸出端也能在讀地址復(fù)位的地方進(jìn)行復(fù)位,保證輸出的音頻塊與輸入端對應(yīng),本設(shè)計(jì)提出了利用一個地址寄存器寄存寫地址復(fù)位時的寫地址,并利用該地址作為讀地址指針更新參考,這樣就增加了讀取數(shù)據(jù)的可靠性。

圖3是改進(jìn)的(讀寫?yīng)毩?fù)位)異步FIFO結(jié)構(gòu)。

3.2 設(shè)計(jì)仿真

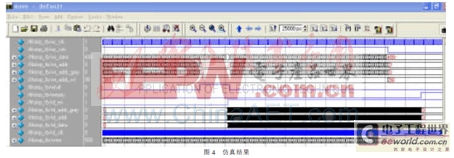

系統(tǒng)設(shè)計(jì)時,利用Quartus II進(jìn)行RTL級的邏輯設(shè)計(jì)并綜合處理,然后設(shè)計(jì)仿真平臺[5],利用Modelsim仿真工具對整個系統(tǒng)進(jìn)行門級仿真。根據(jù)設(shè)計(jì)的異步FIFO 的工作特性,仿真平臺對FIFO工作到滿狀態(tài)、空狀態(tài),以及寫指針復(fù)位后的讀操作進(jìn)行了較全面的覆蓋。

下面是測試平臺的激勵生成代碼:

always #40 wr_clk=~wr_clk;

always #10 rd_clk=~rd_clk;

always @(posedge wr_clk) begin

if(!rstn) begin

wr_data=0;

cntw=0;

rd_en=0;

wr_en=0;

end

else if(cntw==400) begin

rd_en=1;

cntw=cntw+1;

end

else if(cntw==500) wr_rstn=0;

else begin

wr_en=1;

wr_rstn=1;

wr_data=wr_data+1;

cntw=cntw+1;

end

end

代碼的功能是在較低的時鐘速率下,先進(jìn)行寫操作,等到確保寫滿后(即計(jì)數(shù)達(dá)到400時),以高速的讀操作來讀取數(shù)據(jù),并繼續(xù)寫數(shù)據(jù)。當(dāng)計(jì)數(shù)到500時,對寫操作復(fù)位,此時的復(fù)位地址是98。

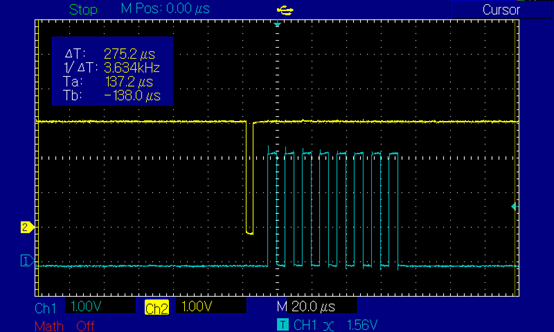

根據(jù)上述的改進(jìn)方法,設(shè)計(jì)、仿真完成后,用Altera公司的Cyclone Ⅲ系列EP3C10E144C8芯片實(shí)現(xiàn)電路程序設(shè)計(jì)。仿真結(jié)果如圖4所示。在圖中可以看到,wr_addr_rst的值一開始默認(rèn)為383,但寫入端有寫復(fù)位時,即為寫復(fù)位時的地址值98,該值也即作為讀操作的地址復(fù)位參考值傳遞到讀操作模塊。等到讀操作進(jìn)行第二輪讀取并讀到第98個地址時,再復(fù)位到0地址時,仿真完成。

本文基于FPGA內(nèi)部存儲器,提出了一種針對視音頻解嵌系統(tǒng)更具效率的異步FIFO,對通用的FIFO進(jìn)行改進(jìn),并利用硬件描述語言及相應(yīng)的仿真工具實(shí)現(xiàn)了功能仿真。仿真結(jié)果表明,本設(shè)計(jì)能很好地按照設(shè)計(jì)的意圖工作。此外,還針對視音頻解嵌系統(tǒng)中,音頻塊輸出端異步FIFO提出了寫復(fù)位地址寄存,讀地址根據(jù)此寄存值來進(jìn)行更新及復(fù)位的改進(jìn),提高了異步FIFO的工作效率和可靠性。

參考文獻(xiàn)

[1] Working group on digital input-output interfacing.數(shù)字音頻AES3接口標(biāo)準(zhǔn)——線性表示雙信道數(shù)字音頻數(shù)據(jù)的串行傳輸格式[J].劉欣榮譯.有線電視技術(shù),2003(8).

[2] AVE W H, PLAINS W. SMPTE292M, television bit2 serial digital interface for high2 definition television systems[S]. NY,10607(914):761-1100.

[3] 汪東,馬劍武,陳書明.基于Gray碼的異步FIFO接口技術(shù)及其應(yīng)用[J].計(jì)算機(jī)工程與科學(xué),2005(11).

[4] 王淼,宋晗.異步FIFO的FPGA實(shí)現(xiàn)[J].微處理機(jī),2004(8).

[5] NAVABI Z.Verilog數(shù)字系統(tǒng)設(shè)計(jì)——RTL綜合、測試平臺與驗(yàn)證(第二版)[M].李廣軍,等譯.北京:電子工業(yè)出版社,2007.

評論