以Flash為基礎的FPGA實現高度安全設計

對電子系統而言,FPGA的保密性極其重要。圖1列出了兩個系統設計的示意圖,左邊為1995年所作的系統設計,在該設計中,以ASIC芯片為核心,FPGA僅起到膠合邏輯的作用;在右邊2005年進行的同類型系統設計中,不難發現FPGA已經成為系統設計的核心,它整合了原有ASIC及部分ASSP芯片的功能,因此FPGA作為系統芯片直接取代了ASIC的功能。隨著FPGA性能、容量與功能的不斷提升,今天的FPGA 已成為系統的心臟、知識產權的集合,所以如果FPGA存在安全性問題的話,與其相關的產品將遭受嚴重打擊。

保密性定義——四個對FPGA最大的安全威脅

a.克隆

克隆是指競爭對手拷貝啟動 PROM 或從

板上攔截處理器碼流并進行復制。如果設計中包含外部碼流時,則該設計的IP 對克隆非常脆弱。

b.反向工程

反向工程即競爭對手由重建您的設計原理圖或網表復制您的設計。在這個過程中,競爭對手將了解設計的運作從而進行改進。

c.過建

過建在把您的產品交給無道德的合同制造商生產時出現,這些制造商能在開放市場上購買額外的FPGA元器件,然后在廠家沒有允許的情況下,生產額外的產品,在沒有開發成本和不需要提供技術支持的條件下,以更低的價格在市場上售賣,從而牟取利潤。

d.拒絕服務

拒絕服務屬于惡意破壞的行為,您的競爭對手或者黑客能夠通過重新編程您系統上的 SRAM FPGA而使您的系統不能運行。拒絕服務使廠家的聲譽、產品的質量等形象將遭到破壞。

Actel 第三代 FLASH FPGA

在了解了保密性的定義及FPGA保密重要性的基礎上,Actel推出了第三代Flash FPGA,具有眾多優點與特性。

Actel第三代Flash FPGA,包括兩個產品系列:ProASIC3與ProASIC3E。ProASIC3能實現30k到1M的門密度,它的容量高達144kb SRAM,具有288個 I/O ;ProASIC3E能實現600k到 3M的門密度,它的容量高達504kb SRAM,具有604個I/O。

這兩個系列均具備增強的高性能結構,其時鐘頻率最高可達350MHz,相對于第二代產品來說,其封裝密度提高了20%,而邏輯利用率超過95%。SRAM的工作頻率也可達到350MHz,而且每個模塊中均帶有硬連線的FIFO控制功能。三個鎖相環(PLL)的輸出頻率也可達到350MHz,并且具有靈活的相位輸出、延遲、分頻和倍頻功能。這兩個系列同樣支持64 位、66 MHz的PCI總線。

作為以價值為基礎的FPGA,第三代產品提供了全新的功能,包括:所有器件都帶有1kb片上可配置的Flash ROM及帶硬連線 的AES 解密安全 ISP。上一代產品中的FPGA的保密措施在這一系列內繼續保持,如片上 FlashLockTM 安全措施及針對單電壓工作而在片上集成的電荷泵。最后,需要提及的是產品支持19種不同的I/O標準,包括 LVDS等。Actel第三代Flash FPGA具有競爭性的成本優勢,因為Flash 技術可省去SRAM FPGA額外的成本負擔。此外,Flash 技術還可以提供以下獨特的性能: ·單芯片;

·高安全性;

·上電即行;

·高可靠性 / 固件錯誤免疫性;

·低功耗;

·高性能。

Actel FLASH FPGA的保密性特點

保密性特點

Flash FPGA的物理結構與保密性

由于Flash非揮發性的特點,所以基于Flash 架構的FPGA在一個可靠的環境下被編程以后,就不再需要一個另外的碼流,因此它不會受到克隆這種攻擊方式的威脅。另外,它對反向工程等入侵性攻擊有高度的

抵抗性,這是因為在Flash FPGA里面的用戶邏輯完全取決于Flash晶體管的內容,就算把器件解體或剝離也只能顯露器件內部結構,而不是 Flash 晶體管的實際內容。由于Flash FPGA表面的一致使它受到入侵性攻擊時,很難辨認其探針點。

A3P/E的保密特性

FlashLock可以保證器件上的保密設定不被隨便更改 ,它包括一個對應的密鑰,長度為128位,其揭露密鑰所需的時間為5.4x1023年,因此十分可靠。它還包括永久FlashLock及編程文檔的AES加密,其AES密鑰長度為128位,而揭露此密鑰所需的時間將長達149萬億年。

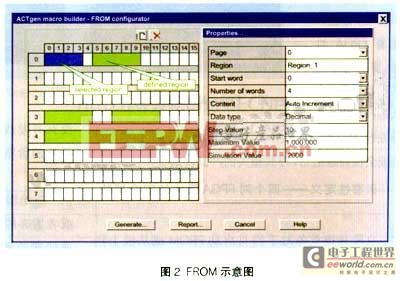

Flash ROM (FROM) 的特性及應用

第三代Flash FPGA是唯一帶片上Flash ROM (FROM)的FPGA,其FROM總共有1024位,分為8個頁,每頁的寬度為128位,見圖2。它的應用非常廣泛,包括:互聯網協議尋址、設備序列編碼、訂閱模式、系統校準設定、安全的加密匙存儲、資產管理跟蹤、用戶喜好存儲、日期標志及版本控制等。

保密性功能選項

在新FPGA上進行保密設計時,有幾種不同的保密性功能選項可供選擇:一、只利用FlashLock密鑰進行保護 (沒有AES加密),在這個選項下,用戶可選擇只保護FROM、只保護FPGA陣列或兩者同時保護。二、AES 加密加 FlashLock 密鑰保護,在這個選項下,AES 密鑰一直受到FlashLock密鑰保護,所以被AES加密過的文件不會包含FlashLock密鑰。三、只加密 FROM、只加密FPGA陣列或兩者同時加密,在這個選項下,可以獨立地更新FROM及FPGA 或對其編程。編程的格式可以為純文本格式的 STAPL 文件或經 AES加密過的STAPL文件,在這兩種STAPL 文件里,可以只包括 FROM、FPGA陣列或兩者同時包括。

保密報頭

保密報頭包含兩種密鑰:FlashLock密鑰及AES密鑰,它也包括FROM及FPGA列陣的信息認證控制。它還包括FPGA陣列與FROM的保密設定。具體的FPGA陣列保密設定包括:寫入、擦除及校驗的存取控制與加密/不加密的存取控制 (寫入、擦除及校驗);FROM的保密設定包括:寫入、擦除及讀取的存取控制(在此情況下校驗是一直被允許的)與加密/不加密的存取控制 (寫入、擦除及讀取)。

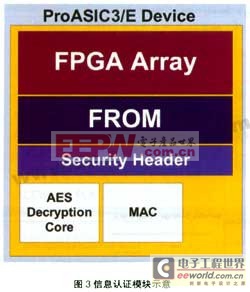

信息認證模塊(MAC)

信息認證模塊負責認證整個編程碼流,見圖3,包括AES解密核心把STAPL文件解密;MAC檢查解密后的數據是否可被認識:如果正確,器件就可以被擦除及編程;如果不正確,軟件會防止編程序列被啟動。在認證進行過程中器件仍可正常工作。

另外該模塊還負責在編程數據傳進器件時檢驗是否存在損壞的數據,具體做法是在編程前對每個數據包進行驗證。

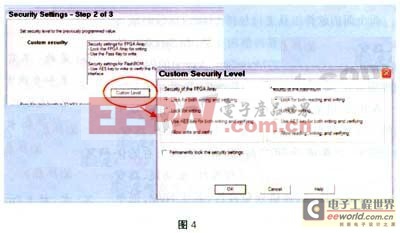

實施保密的軟件設置

以下我們將介紹如何進行保密的軟件設置,首先定制安全級別,如圖4所示:

用戶可在生成安全文件時,選擇“Custom Level”選項,將彈出“Custom Security Level”對話框,即可看到FPGA陣列與FROM的保密設定選項,具體的選項包括:

——只容許在 FLASHLock 密鑰正確時寫入、擦除及校驗;

——只容許在 FlashLock 密鑰正確時寫入、擦除(校驗可以在沒有 Fl

ashLock 密鑰下進行);

——只容許在器件內有正確的AES密鑰時進行寫入、擦除及校驗(配置器件在重編程和校驗FPGA陣列時接受一個被加密的編程文件);

注意:a.要求在器件內有包含正確的AES密鑰;b.FlashROM在這個模式下讀取被禁止;c.加密過的FlashROM內容只允許進行校驗。 ——接受沒有FlashLock或AES密鑰的純文本STAPL 文件的寫入、擦除、讀取 (Flash ROM) 及校驗。其次,設定保密包頭,如圖5所示:

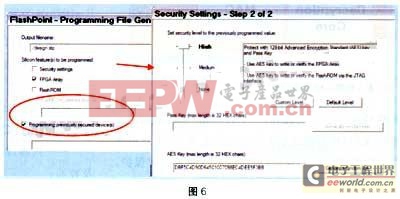

在申請編程文件時點擊選擇“Security Settings”選項,在彈出的對話框中選擇期望的保密設定,并輸入FlashLock密鑰 (即軟件里的Pass Key) 及AES密鑰即完成了保密包頭的設定。最后,編程生成加密編程文件,如圖6所示。

為加密編程設定STAPL文件的具體步驟是:點擊選擇“Programming previously secured device(s)”選項,在彈出的對話框中點擊“FPGA Array Only”或“FlashROM Only”選項,或者兩者并選。最后,在彈出的“Security Settings ”對話框中的相應位置提供預編程時所用的同一個AES密鑰。

完整的解決方案

為了配合ProASIC3與ProASIC3E,Actel提供了全面的硬件工具支持。新推出的低成本ISP編程器、啟動工具套件(Libero Gold、FlashPro3、評估板及教程指南和文檔)、可進行批量編程的Silicon Sculptor及其他調試工具,如First Silicon Solution的Logic Navigator邏輯分析器及Synplicity的Identify RTL調試器等。

而全面的軟件工具支持包括:Libero 7.0(Gold 版可從網站免費下載)及業界提供的支持,如Synplicity的Synplify、Mentor Graphics的ModelSim、Magma的PALACE物理綜合及WaveFormer Lite的Reactive Testbench等。

Actel公司第三代以Flash為基礎的FPGA,除了高的安全性與保密性外,也是一個面向大批量生產的FPGA,它集成了ASIC與SRAM FPGA所有的優點,包括:單芯片上電即行、非揮發性、低功耗、高安全性、高保密性、固件錯誤免疫性、片上NVM、低單位成本、低總系統成本、無 NRE費用、可快速構建原型、快速的生產交貨期及系統內可編程等諸多優點。

評論