基于FPGA的基帶64×64數據分配矩陣設計方案

3.2.2 譯碼模塊設計

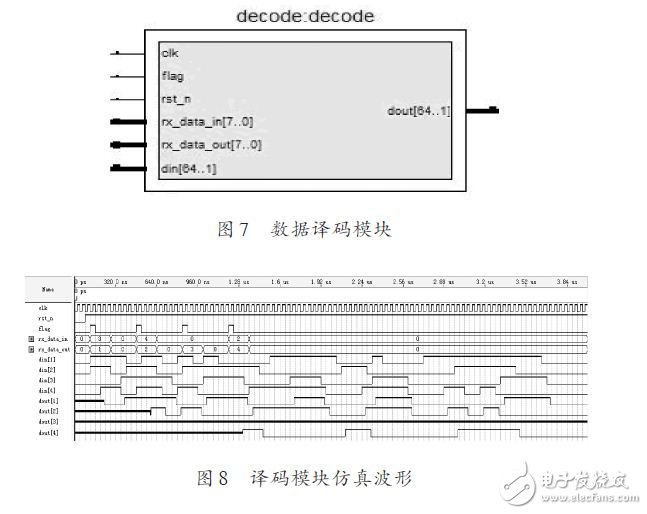

本文引用地址:http://www.104case.com/article/221565.htm譯碼模塊的模塊化框圖如圖7所示,其功能是對上位機發送的輸入輸出端口編號進行譯碼,使相應的輸入端口和輸出端口連通,如檢測到flag 有效的情況下,rx_data_in為2,rx_data_out為3,則該模塊會將din[2]通道的輸入信號經dout[3]輸出通道輸出。部分代碼如下[10]:

![則該模塊會將din[2]通道的輸入信號經dout[3]輸出通道輸出。部分代碼如下[10]:](http://editerupload.eepw.com.cn/201402/98f23960cbfc37a6c4c0aa38b05dfbbc.jpg)

3.2.3 譯碼模塊仿真

由于64×64的仿真很繁瑣且不易操作,所以對4×4的譯碼模塊進行仿真,仿真結果如圖8所示,輸出1與輸入3相連,輸出2與輸入4相連,輸出3懸空,輸出4與輸入2相連。

4 結語

本文采用FPGA作為實現控制邏輯的核心部件,提出了基于FPGA的基帶64×64 數據分配矩陣設計方案,并介紹了上位機的軟件設計思路和FPGA的內部編程實現及仿真。經驗證本系統基本能實現基帶數字信號的分配路由,從而證實了該方案具有規模大、成本低、高速等特點,可廣泛應用于大規模基帶數字系統測試及信號程控分配調度中。

fpga相關文章:fpga是什么

晶振相關文章:晶振原理

評論