基于FPGA的幀同步系統設計方案

2.1 總體結構設計

根據實例需求,幀同步碼組長度(LenCode)、幀同步碼組(FrameCode)、容錯位數 (ErrorNum)、幀長(Len-Frame)、校核態校核幀數(CheckNum)以及同步態校核幀數(SyncNum)均以常量的形式設置,便于 VHDL程序中修改同步參數。系統數據速率及時鐘頻率為50 MHz.

根據圖2所示的結構,很容易想到采用狀態機的設計方法來實現同步系統。不論是采用狀態機方式,或原 理圖方式進行VHDL程序設計,最終均可以轉換成VHDL代碼的形式。顯然,直接采用編寫VHDL代碼的形式,更利于程序的修改及升級維護。因此,本文完 全采用代碼編寫方式來進行程序設計。

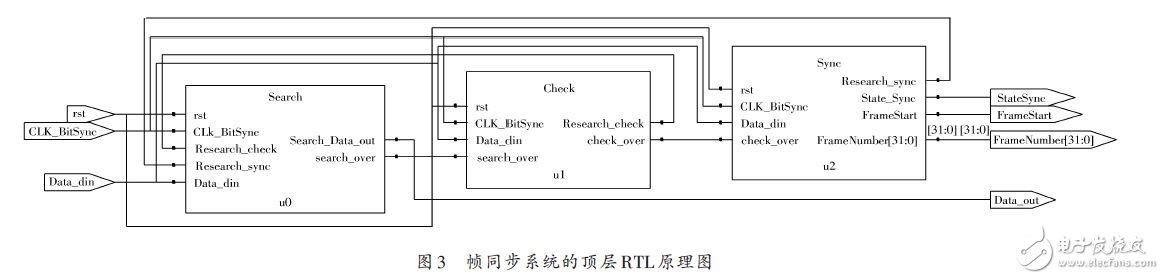

圖2是一個典型的狀態轉移圖,可以將轉移條件看作狀態之間的信號接口。 整個幀同步系統可以劃分為搜索狀態模塊(Search)、校核狀態模塊(Check)及同步狀態模塊(Sync)。除了上電后啟動搜索狀態之外,當校核未 通過(CheckNum 幀內有一個校核幀未同步)或同步態失鎖(連續SyncNum 幀未同步)時也需啟動搜索狀態,因此搜索狀態的啟動信號有復位信號(rst)、校核態重搜索信號(Research_check)和同步態重搜索信號 (Research_sync);校核態的啟動信號僅來自于搜索態(search_over),即只有當搜索到幀同步碼后才能轉入校核態,如果校核通過則 送出校核完成信號(check_over),校核未通過則送出重新搜索信號(Research_check);同步態的啟動信號僅來自于校核態 (check_over),只有校核通過后才能進入同步狀態。進入同步態后,持續對同步碼組進行檢測,當檢測到重新失鎖后送出 Research_sync,重新啟動搜索狀態。圖3為幀同步系統頂層VHDL程序文件采用Synplify Pro綜合后的RTL原理圖。

2.2 搜索模塊的VHDL設計與仿真

搜索模塊的對外接口如圖3所示。其中,CLK_BitSync及Data_in分別為位同步時鐘信 號和輸入數據;Data_out為經2個時鐘周期延時后的比特流數據。對輸入數據的延時處理,是為了補償產生search_over 時的處理時延,以便于脈沖信號search_over 與最后一位幀同步碼對齊。

搜索輸入比特流中的幀同步碼組,首先需要將輸入數據送入移位寄存器(Regdin)中,而后將 Regdin中的數據與幀同步碼組相比即可。程序中將多路啟動信號(rst、Research_check、Research_sync)取或后,作為異 步復位信號,用于啟動一次搜索過程。搜索過程中,采用for循環對寄存器Regdin 與同步碼組進行比較,通過逐位比較,每發現1 b不相同,則計數加1,計算出兩者之間的漢明距離。計算完漢明距離后,判斷是否大于容錯門限ErrorNum,如大于容錯門限則繼續搜索,否則輸出同步脈 沖search_over,并停止搜索。

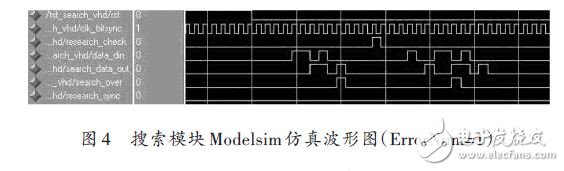

圖4為搜索模塊的Modelsim仿真波形。其中,幀同步碼長度LenCode=7, 幀同步碼FrameCode=“1011000”,容錯門限ErrorNum=1.可以看出,復位后首先搜索到一次幀同步碼組;當 Research_check為高電平,啟動另一次搜索過程,比特流中搜索到“1001000(ErrorNum=1)”時,此時容錯位數設置為1,因此 輸出同脈沖search_over,并停止搜索過程,即使后續比特流中出現了“1011001(ErrorNum=1)”,仍然不輸出同步脈沖。

2.3 校核模塊的VHDL設計與仿真

為便于程序編寫,校核模塊主要由Check_Ce 進程和Checking 進程組成。Check_Ce 進程用于檢測search_over信號,檢測到信號出現高電平后,產生長度為CheckNum 幀數據的高電平允許信號CheckCe,并通過計數器Number 來標識每幀中數據及同步碼組的位置。產生了CheckCe及Number信號后,Checking進程只需在CheckCe信號為高電平的范圍內對同步碼 組進行校核即可。校核完成后,需要使check_over(連續CheckNum幀均同步)或research_check(CheckNum幀內有一幀 未同步)信號產生一個高電平脈沖。幀校核的方法與搜索同步碼組的方法類似,即通過漢明距離來判斷是否同步。將校核態分成Check_Ce進程和 Checking進程來分別進行實現,則每個進程的功能劃分更為簡單,編程實現時也相對容易得多。

fpga相關文章:fpga是什么

評論