基于FPGA的速率自適應圖像抽取算法

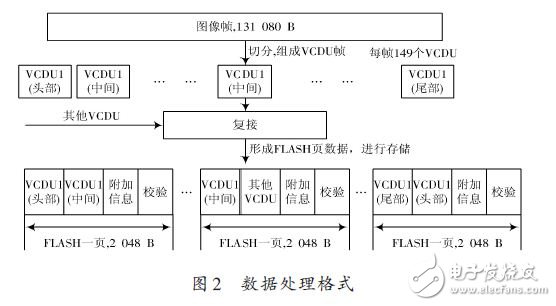

FLASH的讀寫都基于頁進行操作,讀出一頁的兩個VCDU中,有多種可能性,數據處理過程如圖2 所示,圖2中給出三種可能,一是前一個是需要抽取的頭數據,后一個是需要抽取的中間數據;二是前一個是需要抽取的圖像數據,后一個是不需要抽取的其他 VCDU 數據;三是前一個是需要抽取的尾數據,后一個是下一幅圖像的頭,但不需要抽取。

本文引用地址:http://www.104case.com/article/221482.htm

可見,在抽取回放中必須濾除一定數據,保證抽取圖像的完整性和正確性,因此在存儲時增加附加信息,以解決圖像完整性問題。

附加信息設計為6 b,格式定義見表1.

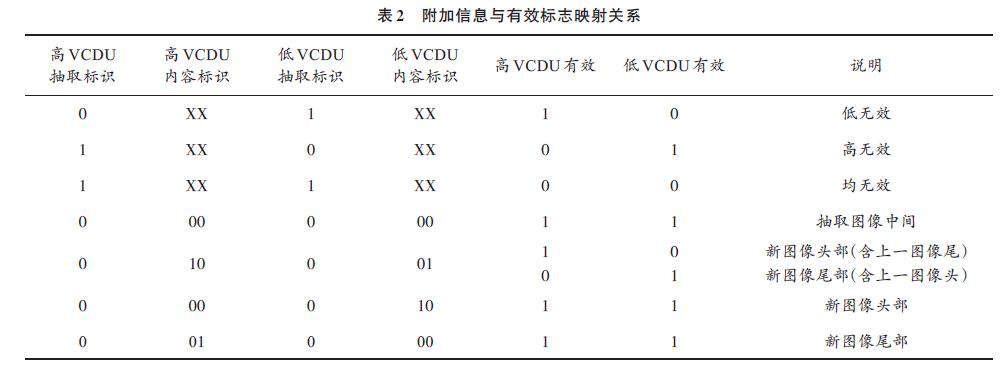

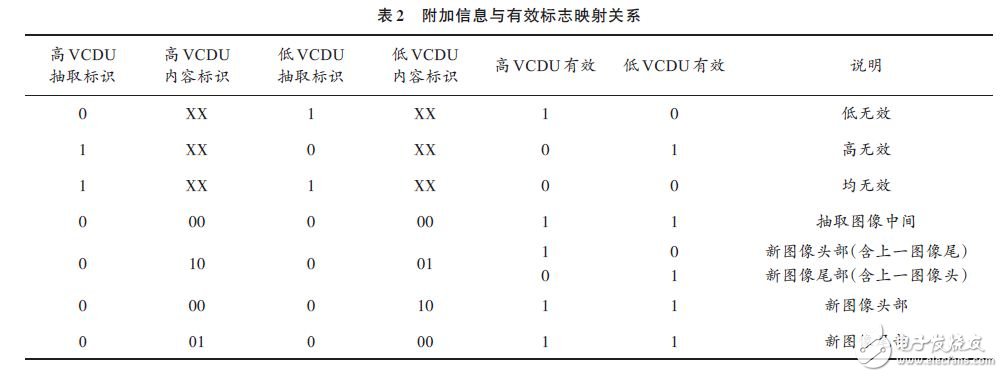

附加信息與數據一起被存到存儲芯片中。在回放時,讀取附加信息,解析出高VCDU有效/無效信號和低VCDU有效/無效信號。由回放請求模塊進行數據濾除,保證僅回放有效數據,并且為完整圖像。

附加信息與有效標志映射關系見表2.對輸入數據的各種情況,按照表2中映射關系解析出有效/無效信號。

數據過濾模塊設置緩存,根據高低VCDU有效標示控制緩存地址,為1進行讀取,為0跳過無效的VCDU數據,實現數據的濾除。

1.2 實時性設計

方法中必須獲取到幀頭VCDU 信息和幀尾VCDU信息才會更新圖像數據幀地址寄存器,即在收到一整幅圖像之后才能進行回放。

抽取的延時計算一幅圖像第一比特輸出和輸入時間之差,最壞情況時第N 幅圖像已經寫入,第N + 1 幅圖像尾部沒有寫完,即在第N 幅圖像頭寫入后兩幅圖像時間才開始回放。抽取過程中延遲時間=兩幅圖像時間+數據回放時間。工程中,圖像生成速率為10幅/s,一幅圖像的生成時間按 100 ms計算。

回放數據的時間為數據從FLASH芯片中讀出時間和數據緩存時間,每頁2 KB,讀取時間約320 μs;其余處理路徑上的寄存時間《10 μs.因此,抽取過程中延遲時間約為200.33 ms ,完全可以滿足圖像的回放觀看需要。

fpga相關文章:fpga是什么

存儲器相關文章:存儲器原理

評論