基于FPGA多路機載冗余圖像處理系統的設計方案

(2)數據流選擇模塊

本文引用地址:http://www.104case.com/article/221481.htm根據需要選擇兩路輸入視頻信號中的一路進行輸出。

(3)SDRAM乒乓操作和控制模塊

由于SDRAM 乒乓操作具有節省緩沖區空間、流水線式算法以及低速模塊處理高速數據流的特點。因此,本設計采用乒乓操作SDRAM.

SDRAM 作為整個圖像處理系統的緩存,起著至關重要的作用。它將外部輸入的圖像按幀存入SDRAM中,然后按幀將圖像數據送到外部繼續處理。FPGA的控制邏輯所需要完成的功能有:接收來自外部的圖像數據,并進行緩沖和數據重組,產生符合SDRAM控制器位寬的數據信號;產生對SDRAM 的讀、寫命令和地址,并將它們寄存在FIFO中,隨時供SDRAM控制器提取。因此,系統需要一個地址產生邏輯;對SDRAM進行直接控制,將用戶產生的地址命令進行解析,產生讀/寫、刷新等一系列操作,對SDRAM 發出的各種命令要符合特定的時序要求。在上電的時候還必須完成對SDRAM的初始化工作;建立用戶與SDRAM 的數據通道,在SDRAM和用戶接口之間傳遞需要寫入或者讀出的數據,并且調整對應讀/寫操作的DQS信號時序,使其滿足SDRAM的要求;緩存從 SDRAM中讀出的數據,由于直接讀出的速度非常高,直接處理會對后端產生很大的壓力。因此,需要進行緩存之后才送到后續處理。

(4)輸出時序生成模塊

這部分模塊的主要功能是對SDRAM 進行操作,生成需要的視頻時序信號以及生成驅動液晶屏的視頻信號。

2.2.2 SDRAM操作

為了滿足前后端數據流匹配,并實時發送,這里采用了SDRAM讀寫交替進行的讀寫方式。

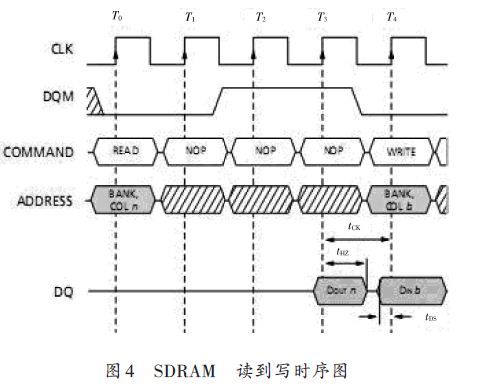

SDRAM 讀到寫時序圖如圖4所示。寫入和讀出操作的發起是由行激活命令開始的,命令為10011,發起的同時sdram_addr送入列地址,發起寫入讀出命令時送入行地址。寫入命令與數據同步,讀出命令在發出后潛伏期時間后送出數據到端口,sdram_data 為SDRAM 的輸入輸出數據端口。預沖方式采用了自動預沖,即在發起讀寫命令時將地址位A10置高就可以在讀寫操作后SDRAM內部自動進行預沖操作,不需要發出額外命令,自動預沖占用4個時鐘周期。

3 仿真分析以及測試結果

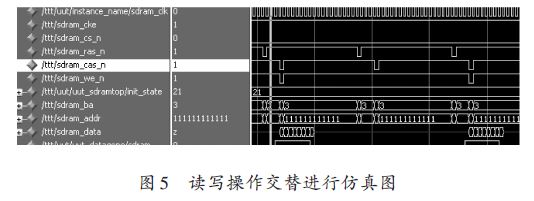

讀寫操作交替進行仿真圖如圖5所示。圖5中包含了兩個寫入操作,一個讀取操作。

評論