基于FPGA多路機(jī)載冗余圖像處理系統(tǒng)的設(shè)計(jì)方案

2.1 SDRAM選擇依據(jù)

整個(gè)系統(tǒng)顯示的分辨率為1600×1200@60 Hz,信號(hào)位為真彩色24b,則一幀圖像所需需要存儲(chǔ)的容量C = 1 600×1 200×24=46 080 000 b≈47 Mb;考慮到SDRAM乒乓操作和容量等問題,選用MICRO公司生產(chǎn)的容量為128M的MT48LC4M32B2TG-6器件,速度等級(jí)6,時(shí)鐘頻率達(dá)到166 MHz.該器件具有32根數(shù)據(jù)線和12根地址線,還有一些控制線。通過在FPGA內(nèi)部搭建邏輯控制單元,可以很好的控制SDRAM 視頻信號(hào)的翻轉(zhuǎn)等操作。

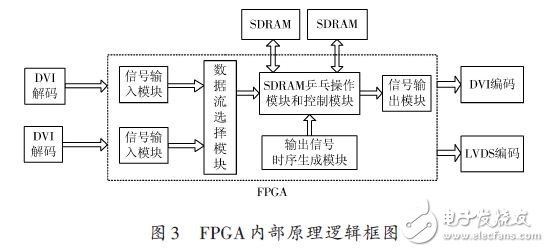

2.2 FPGA內(nèi)部原理邏輯框圖

FPGA內(nèi)部原理邏輯框圖如圖3所示。

2.2.1 FPGA內(nèi)部邏輯功能介紹

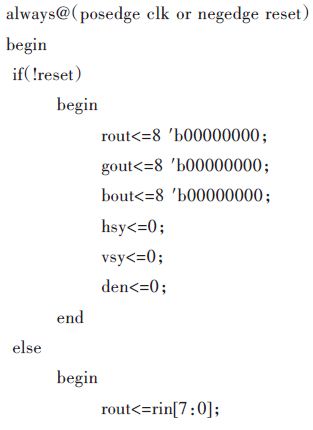

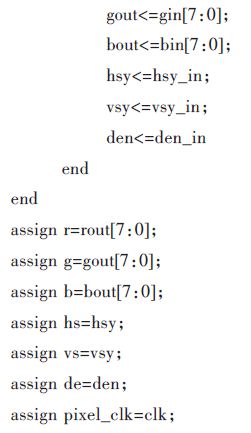

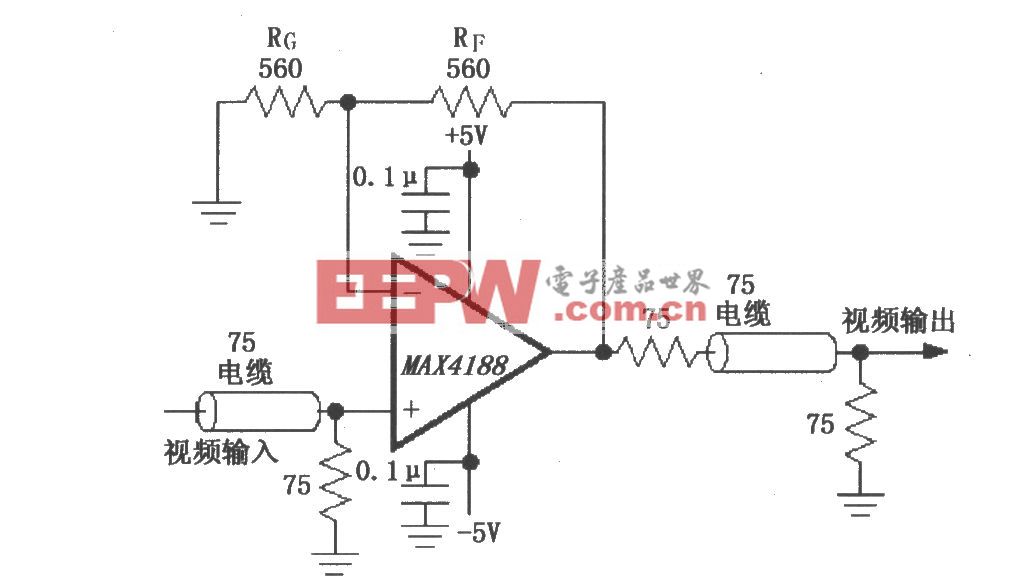

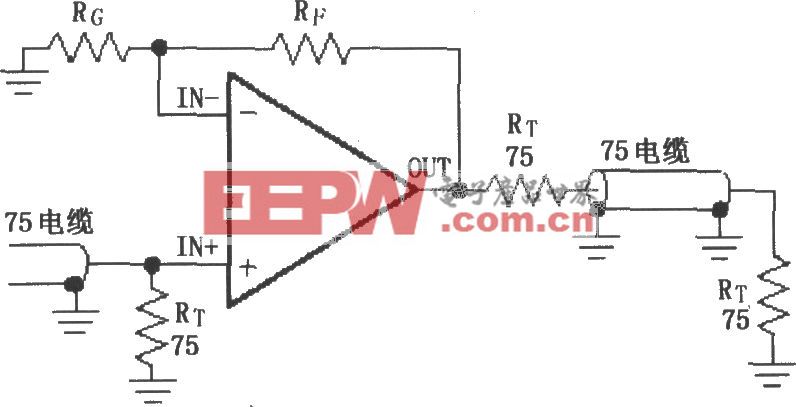

(1)信號(hào)輸入模塊

這部分的主要功能是接收外部輸入的視頻信號(hào),增強(qiáng)輸入信號(hào)的驅(qū)動(dòng)能力,為信號(hào)的后續(xù)處理做準(zhǔn)備。其用Verilog 語言實(shí)現(xiàn)的邏輯代碼如下所示:

評(píng)論