串行RapidIO: 高性能嵌入式互連技術(shù)

在傳統(tǒng)的基站中,DSP與ASIC或FPGA之間的互連一般用外部存儲(chǔ)器接口(EMIF);DSP之間或DSP與主機(jī)之間一般用HPI或PCI互連。它們的主要缺點(diǎn)是:帶寬小、信號(hào)線多、主從模式接口、不支持對(duì)等傳輸。另外,DSP不能直接進(jìn)行背板傳輸。

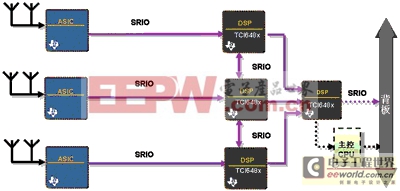

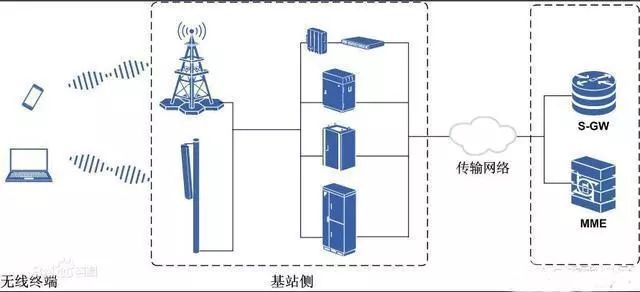

使用SRIO則可有效的解決這些問題,大大提高無線基站的互連性能。圖8顯示了一種無線基站基帶互連框圖。在這里,SRIO實(shí)現(xiàn)了大部分器件之間的互連,甚至可支持DSP進(jìn)行直接背板傳輸。

圖8 SRIO提高無線基站互連性能

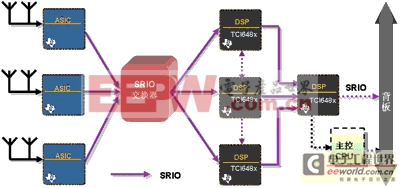

通過SRIO交換器件互連可以進(jìn)一步提高基帶處理的靈活性,圖9顯示了一種基帶SRIO交換互連的框圖。這種互連有利于實(shí)現(xiàn)先進(jìn)的基帶處理資源池架構(gòu),數(shù)據(jù)可被送到任何一個(gè)通過SRIO交換器互連的處理器中,從而達(dá)到各個(gè)處理器的負(fù)載均衡,更加有效的利用系統(tǒng)的整體處理能力。

圖9 SRIO交換為無線基站基帶處理提供更大的靈活性

綜上所述,對(duì)嵌入式系統(tǒng)尤其是無線基礎(chǔ)設(shè)施,串行RapidIO是最佳的互連技術(shù)。高達(dá)10Gb/s的帶寬、低時(shí)延和低軟件復(fù)雜度滿足了飛速發(fā)展的通信技術(shù)對(duì)性能的苛刻需求;串行差分模擬信號(hào)技術(shù)滿足了系統(tǒng)對(duì)引腳數(shù)量的限制,及對(duì)背板傳輸?shù)男枨螅混`活的點(diǎn)對(duì)點(diǎn)對(duì)等互連、交換互連,和可選的 1.25G/ 2.5G/3.125G三種速度能滿足多種不同應(yīng)用的需求。

評(píng)論