基于McBSP的高速串行數據采集系統設計

2.2 AD974工作原理

1. 主要引腳定義(表1)

表1 AD974的引腳功能

引腳號 | 引腳號 | 功 能 說 明 |

2-5,25-28 | VXA,VXB | 模擬輸入范圍選擇端。 |

6 | BIP | 雙極性偏移量。連接VXA輸入以提供雙極性的輸入范圍 |

7 | CAP | 參考緩沖輸出。 |

8 | REF | 參考輸入/輸出端。 |

10 | R/C | 讀取/轉換輸入端。用于控制轉換和讀模式。 |

12 | PWRD | 掉電模式輸入端。 |

13 | EXT/INT | 數字時鐘選擇輸入端,決定采用內部時鐘還是外部時鐘。 |

15 | SYNC | 數字輸出幀同步端。只有在使用外部時鐘時它才起作用。 |

16 | DATACLK | 串行數字時鐘輸入或輸出端。 |

17 | DATA | 與DATACLK同步的串行數字輸出端。 |

18,19 | WR1,WR2 | 多路轉換器寫輸入端。 |

20 | CS | 片選輸入端 |

21 | BUSY | 忙狀態信號輸出端。 |

2. 工作原理

AD974的模數轉換由R/C、CS兩信號來控制。在R/C降為低電平時,若CS也為低電平,在至少經過50ns后,輸入信號將被保留在內部的電容陣列上并準備開始轉換。一旦轉換開始,BUSY信號將變為低電平直到轉換完畢。在內部,信號R/C和CS需進行或操作,但是對哪一個信號先變為低電平做為開始轉換的標志并沒有嚴格要求。唯一的要求是這兩個信號變為低電平的時間延遲不得少于10ns。轉換完畢后,BUSY信號返回高電平,另一方面,AD974準備下一次轉換以確保能繼續跟蹤輸入信號。在某些情況下,將CS引腳保持低電平,而將R/C用于決定是開始轉換還是讀取數據。需要指出的是,在AD974上電后進行首次轉換時,其DATA輸出將是不確定的,轉換輸出需要經過一定時間之后才能穩定下來。模數轉換可以使用由AD974的內部時鐘,也可以使用外部時鐘,這并不影響轉換結果的連續性。如果EXT/INT為低電平,則AD974被設置為內部數據移位時鐘模式;相反,如果EXT /INT為高電平,則AD974被設置為外部數據移位時鐘模式。

3. DSP McBSP

3.1 McBSP的工作原理

McBSP口進行串行通信時,使用的外部接口管腳有:DR,DX,CLKX,CLKR,FSX,FSR,CLKS。DR和DX分別用來進行數據的收發。 CLKX,CLKR,FSX,FSR,CLKS為數據傳輸提供可靠的時鐘。CLKX,FSX為發送的數據時鐘和幀同步時鐘,CLKR,FSR為接收的數據時鐘和幀同步時鐘,CLKS提供系統時鐘。在收發時鐘的控制下,DSP進行數據的接收和發送。為使DSP按照一定的方式進行通信,要對McBSP的各個控制寄存器進行相應的配置。其中,SPCR0/SPCR1用于設置工作模式、檢測工作狀態、進行收發的復位和啟動。RCR0 /RCR1,用于控制接收數據的幀格式、數據延遲。XCR0/XCR1用于控制發送數據的幀格式、數據延遲。SRGR 0/SRGR1用于控制收發數據時鐘和幀同步時鐘的模式,如大小、極性等。PCR用于控制相應管腳的工作模式。

4. AD974與TMS320C6711 McBSP的接口設計

AD974符合SPI(Series Protocol Interface)數據通訊協議。SPI是一個4根信號線的串行接口協議,包括主/從兩種模式。四個接口信號是串行數據輸入(MISO,主設備輸入,從設備輸出),串行數據輸出(MOSI,主設備輸出,從設備輸入),移位時鐘(SCK)和從設備使能(SS)。SPI接口的最大特點是由主設備時鐘信號的出現與否界定主/從設備間的通訊。一旦檢測到主設備時鐘信號,就開始傳輸數據,時鐘信號無效后,傳輸結束。在這期間,從設備必須被使能(SS信號保持有效)。

TMS320C6711芯片的McBSP的數據同步時鐘具有停止控制選項,因此可以與SPI協議兼容。McBSP支持2種SPI傳輸格式,可以在SPCR寄存器的CLKSTP位中設置。

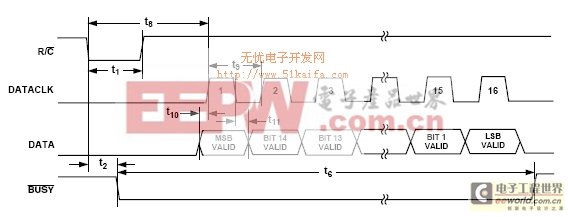

本設計中,我們采用了AD974的內部時鐘模式,其時序圖如圖3。

圖3 AD974內部時鐘模式時序圖

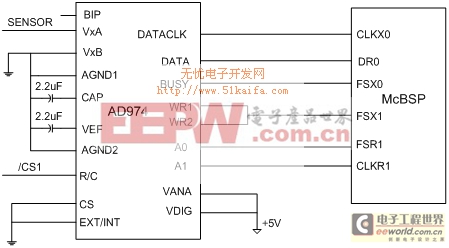

AD974與McBSP的數據傳輸采用SPI從模式進行連接,其接口設計如圖4。

圖4 AD974與McBSP的接口

設計中,我們將AD974的CS片選信號固接為低電平,使芯片一直處于選通狀態。R/C讀/轉信號由地址譯碼器Decoder的/CS1信號(地址 0xB0000000)提供。忙狀態信號端BUSY連接FSX0,串行數字時鐘端口DATACLK連接CLKX0,數據輸入端口DATA連接DR0。多路轉換器寫輸入端WR1和WR2,通道選擇端A0,A1分別與DSP的McBSP1端口的引腳FSX1,CLKR1,FSR1相連。該模塊的具體工作時序如下:

(1) 數據采集開始前,/CS1沒有選通,為高電平,AD974處于寫輸入狀態,通過設置FSX1為低電平,CLKR1和FSR1為所需要的電平可以進行通道選擇。

(2) 數據采集開始時,Decoder選通/CS1信號,設置為低電平。AD974首先鎖存先前選擇的通道號,然后開始進行數據采集和轉換,此時忙狀態信號BUSY由高電平變為低電平。

(3) 由于BUSY信號與FSX0相連,McBSP0作為從設備被使能,等待數據傳輸。

(4) 經過一定的時間,AD974串行數字時鐘有效,并開始進行數據傳輸。McBSP0一旦檢測到時鐘信號,就開始接收AD974傳輸的數據,時鐘信號無效后,傳輸結束。

(5) 數據傳輸完成后,AD974的BUSY信號由低電平變為高電平,從設備無效。

評論