基于高速串行BCD碼除法的數字頻率計的設計

BCD碼減法運算采用行波進位方法,因此必須盡量減小進位邏輯上的延遲。ACEX 1K系列的每個LE中都提供了一個專用的進位鏈和級聯鏈,充分利用這些資源可以提高多位串行BCD碼減法的性能。根據ACEX1K系列周期約束,其延時為:

Tclk=Tco+B+Tsu-(E-C)

式中,Tco為clock-output的延時,Tsu為建立時間,兩個時間均可達到1~2ns;B表示數據延時,為0.6ns;E-C)表示時鐘傾斜[4]。因此,總時鐘延時為4.6ns,即工作頻率可以達到200MHz以上。本文采用100MHz的工作頻率,提高了運算速度。為了減小延時、提高工作效率,在對布局布線進行精確控制以后,把BCD碼減法運算做成模塊,在除法運算過程反復調用,達到了模塊復用效果,大大提高了資源的利用率。

在整個BCD碼除法運算單元,首先通過輸入數據決定信號是否超出測量范圍。

·當ov1為1時,該信號的頻率大于1Hz;

·當NSNX,該信號的頻率大于100MHz;

·當NS=NX,該信號的頻率為1Hz;

·當NS>NX,該信號頻率在測量范圍內。

根據輸入的NS和NX計算輸入信號的頻率。

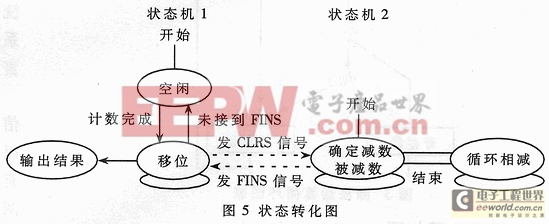

除法運算通過雙狀態機的設計控制一個BCD碼減法運算。所有狀態用同一時鐘進行控制,實現了系統的同步設計,消除了異步邏輯中存在的種種險象。各個狀態之間的關系如圖5所示。當計數模塊完成計數時,則將數輸入除法模塊,開始移位以確定輸入的值;然后發clrs信號到BCD碼減法運算單元開始運算,循環相減。當循環結束時,發回一個HNS信號,部分余數開始移位,進行下一輪的循環。最終輸出FOUT,即運算單元結束。

本頻率計設計采用8位的十進制計數器,隨后應用狀態機實現了高速串行BCD碼除法運算,計算出頻率值。對BCD碼減法模塊的復用,減小了資源的利用。

當今VLSI的發展日新月異,FPGA的容量和速度成倍地增長,而價格卻逐年下降,這將使得基于FPGA設計的數字頻率計優勢更加明顯。相信這一技術必將得到更加廣泛的應用。

評論