基于高速串行BCD碼除法的數(shù)字頻率計的設計

2.2 多位串行BCD碼除法原理

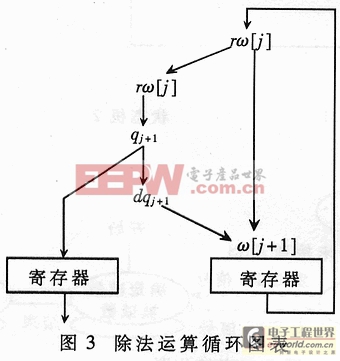

本設計采用循環(huán)式除法運算,循環(huán)原理可以用下面的公式表示[1]:

ω[j+1]=rω[j]-dqj+1

式中,ω[j]為第j步的余數(shù),ω[0]為被除數(shù);d為除數(shù);qj+1為第j+1步所得的商;r為與移位步長有關的常數(shù),在此取為16。

除法運算循環(huán)圖表如圖3所示。

循環(huán)步驟如下:

·將ω[j]左移四位,構成rω[j]。

·通過多次BCD碼減法運算,求得部分商qJ+1,得到部分余數(shù)。

·部分余數(shù)、部分商移位,準備下次循環(huán)。

高速串行BCD碼除法是建立在BCD碼減法運算基礎上的循環(huán)運算。用被除數(shù)減除數(shù)得到部分余數(shù)的BCD碼,如果夠減,則使商加1;否則,余數(shù)和商同時左移四位,并記錄移位的次數(shù)m,根據(jù)對有效位數(shù)的不同要求,可以對m進行賦值,如果要求保留8位有效數(shù)字,則m=8。

在這種循環(huán)除法運算中,減少循環(huán)的次數(shù)是提高運算速度比較有效的方法。在一般循環(huán)式除法運算中,是從低位開始進行循環(huán)相減,循環(huán)次數(shù)等于商。如果是8位除法運行,則得到一個8位的商,要進行8位次的BCD碼減法循環(huán),例如:56895230/8=7111903.8,要進行7111903.8次循環(huán),計算的速度可想而知。

在本設計中借鑒了一般十進制除法的運算方法,從高位開始相減,大大減少了循環(huán)次數(shù)。下面以一個例子說明它的原理:

·將被除數(shù)和除數(shù)移位,使其第一位BCD碼不為0000,并記錄移位的次數(shù)P(例如:56895230/80000000,p=8)。

·比較最高位的大小,如果除數(shù)的最高位大于被除數(shù)的最高位,則將除數(shù)右移4位,同時將P減1(即:56895230/08000000,且p=7)。

·得到的數(shù)盧為小數(shù)點的位置(F:7說明小數(shù)點的位置在第七位數(shù)后)。

·循環(huán)相減。當部分余數(shù)小于08000000,再將部分余數(shù)左移四位,繼續(xù)進行相減。循環(huán)m次后即可得到m個有效數(shù)字的結果,然后根據(jù)p可以確定小數(shù)點的位置。

使用這種方法計算一個8位數(shù)的除法運算,循環(huán)減法次數(shù)最大為80次,每次循環(huán)使用時間為8個時鐘周期。如果工作頻率為100MHz,則最長的運算時間為6.4μs,運算速度大大提高。

圖4

3 設計實現(xiàn)

采用VHL語言設計一個復雜的電路系統(tǒng),運用自頂向下的設計思想[2],將系統(tǒng)按功能逐層分割的層次化設計方法進行設計。在頂層對內(nèi)部各功能塊的連接關系和對外的接口關系進行了描述,而功能塊的邏輯功能和具體實現(xiàn)形式則由下一層模塊來描述。根據(jù)頻率計的系統(tǒng)原理框圖(圖1),運用自頂向下的設計思想,設計的系統(tǒng)頂層電路圖如圖4所示。各功能模塊采用VHDL語言來描述。

在計數(shù)模塊中,通過譯碼完成的信號COMP和標準信號計數(shù)器的溢出信號ov2對門控信號CL進行控制。可以根據(jù)不同的情況選擇門控信號的時間范圍,使設計具有一定的靈活性。采用門控信號CL和被測信號BSN對兩個8位十進制計數(shù)器進行同步控制[3]。根據(jù)D觸發(fā)器的邊沿觸發(fā)的特點,可以將輸入的門控信號CL作為D觸發(fā)器的輸入信號,而將被測信號BSN作為D觸發(fā)器的脈沖控制信號,使觸發(fā)器的輸出端只有在被測信號BSN上升沿時才發(fā)生變化,實現(xiàn)了對使能信號的雙重控制。

本設計比較重要的一部分是運算單元。由于在運算單元中采用的是串行運算,因此其工作頻率必須足夠高。在FPGA中實現(xiàn)時,如何提高串行BCD碼除法運算的速度是比較關鍵的問題。

評論