詳解s3c44b0 cpu 8K cache SRAM的初始化

s3c44b0_flush_cache()函數就這么幾行,代碼如下:

static void s3c44b0_flush_cache(void)

{

volatile int i;

/* flush cycle */

for(i=0x10002000;i0x10004800;i+=16)

{

*((int *)i)=0x0;

}

}

首先莫名的是:計數用的變量i要用volatile來修飾!也許這就是arm或說是嵌入式或說是基于硬件的C程序與基于PC的C程序不同之處吧。加volatile是為了防止編譯器把i給合諧掉 然后就是賦值句*((int *)i)=0x0:這個對寫過或是看過arm程序的都知道吧,不解釋。

然后就是賦值句*((int *)i)=0x0:這個對寫過或是看過arm程序的都知道吧,不解釋。

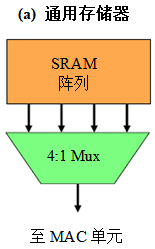

關鍵在于for(i=0x10002000;i0x10004800;i+=16)參看s3c44b0手冊,cache set0:3地址是0x1000000~0x10002000;cache tag0:3+LRU地址是0x10002000~0x10004800。剛開始以為刷新cache是要向cache set0:3寫0,而其實應該向且cache tag0:3+LRU空間寫入0來刷新cache。有點意思的是:cache tag和LRU RAM寫入的地址。(參看s3c44b0手冊關于cache tag部分)由于cache tag和LRU RAM是16字節讀寫的,故i的增加應該是以16為單位的。

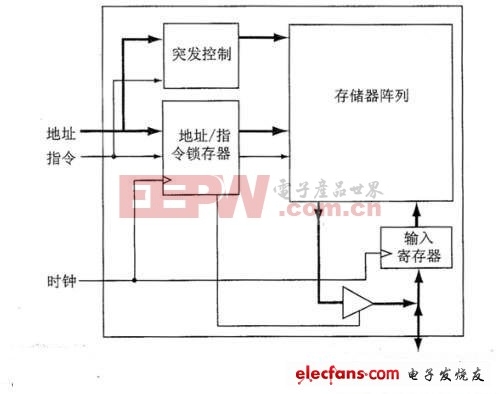

接下來是設置非緩沖區范圍。

NCACHBE0 = 0xC0000000;

NCACHBE1 = 0x00000000;

完全依據程序員個人主觀,呵呵 當然是要好的想法:比如不應該把IO地址放入緩沖區,而應該把它放入非緩沖區;不應該不把SDRAM放入非緩沖區,而應該放入緩沖區。所以,這里把除SDRAM地址外的所有映射地址做為非緩沖區。然后依據地址設置NCACHBE0和NCACHBE1。NCACHBE0在在這里是有用的,高地址為0x0c000000,低地址為0x00000000;而 NCACHBE1可以理解為不用它,所以起始和終止地址都設為0

在設置完之后就只要開啟cpu cache功能就可以。

reg = SYSCFG;

reg |= 0x00000006; /* 8kB */

SYSCFG = reg;

當然,堅持一慣的風格,操作SYSCFG寄存器方式為:讀---操作---回寫。這里把8K內部RAM全作為cache

除了s3c44b0_flush_cache()外,其他都很簡單,呵呵 不是嗎

評論