Cortex—M3的異常處理機(jī)制研究

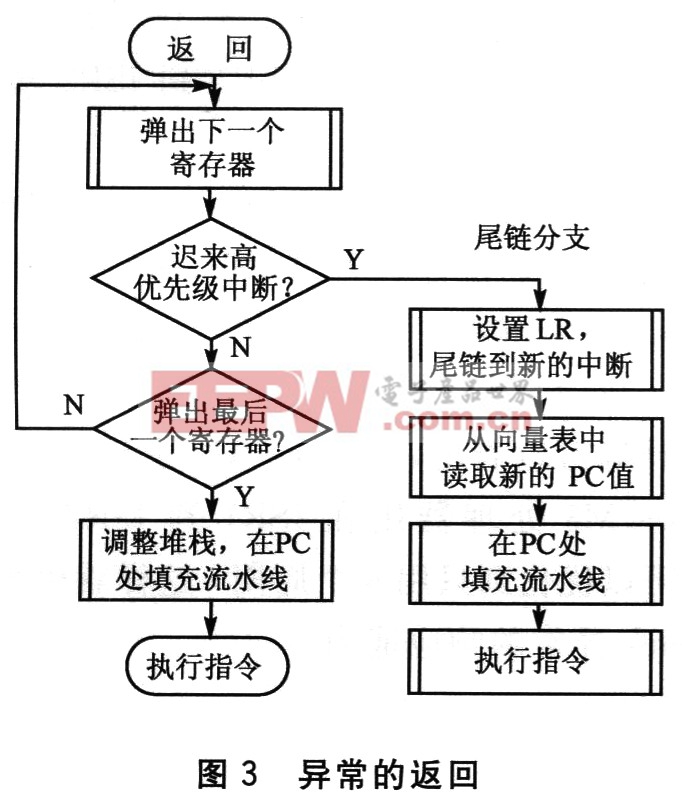

為了應(yīng)對異常返回階段可能遇到的新的更高優(yōu)先級異常,Cortex—M3支持完全基于硬件的尾鏈機(jī)制,簡化了激活的和未決的異常之問的移動,能夠在兩個異常之間沒有多余的狀態(tài)保存和恢復(fù)指令的情況下實現(xiàn)back—to—back處理。尾鏈發(fā)生的2個條件:異常返回時產(chǎn)生了新的異常;掛起的異常的優(yōu)先級比所有被壓棧的異常的優(yōu)先級都高。

尾鏈發(fā)生后,Cortex—M3處理過程如圖3中尾鏈分支所示。這時,Cortex—M3處理器終止正在進(jìn)行的出棧操作并跳過新異常進(jìn)入時的壓棧操作,同時通過Ibus立即取出掛起異常的向量。在退出前一個ISR返回操作6個周期后,開始執(zhí)行尾鏈的ISR。

3 Cortex—M3和ARM7中斷控制器比較

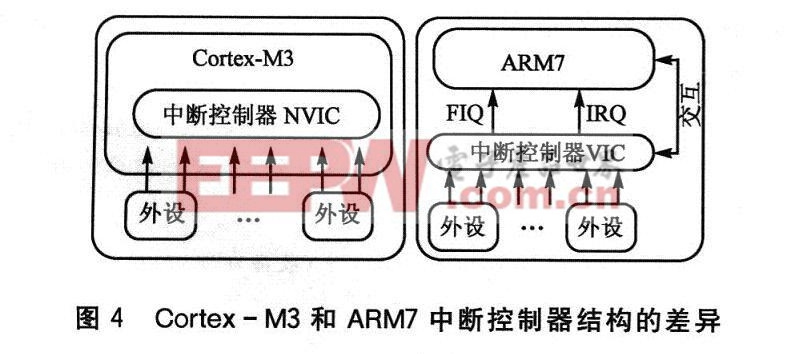

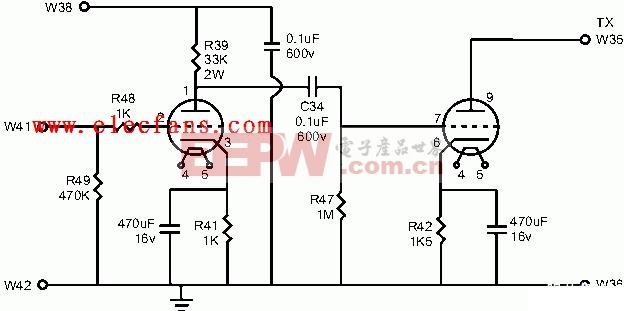

在過去的十年中,基于ARMv4的ARM7系列微控制器廣泛應(yīng)用在各個領(lǐng)域。在ARM7系列中,并沒有對中斷進(jìn)行獨立的服務(wù),而是通過犧牲處理器一定的性能來換取有效的中斷響應(yīng)和中斷處理機(jī)制。Cortex—M3高度耦合的NVIC可以實現(xiàn)硬件中斷處理,同時支持遲到和尾鏈機(jī)制,加快了異常響應(yīng)的速度,充分發(fā)揮了處理器的性能。圖4為Corex—M3和ARM7在中斷控制器結(jié)構(gòu)方面的差異。

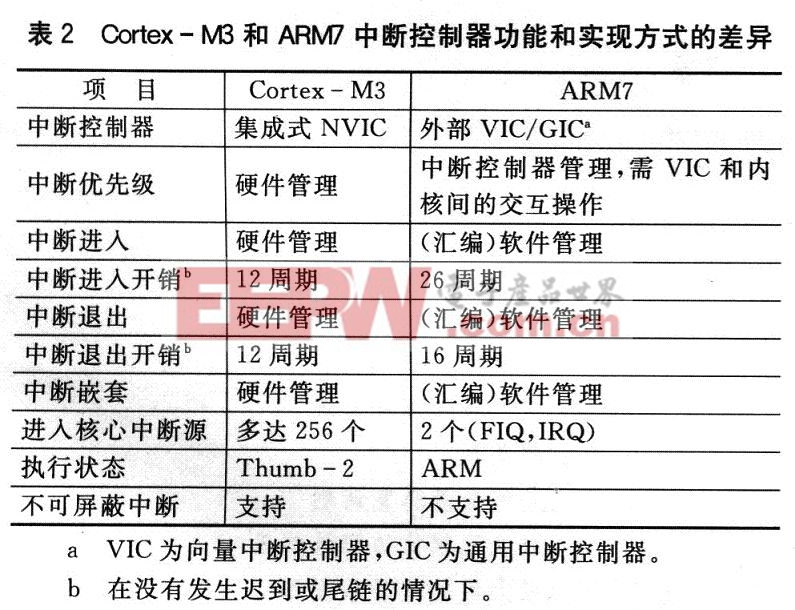

比較可知,NVIC是直接作為Cortex—M3處理器的一部分,集成在處理器核內(nèi)部;而VIC只是游離在ARM7內(nèi)核的外圍,這樣就必然占用內(nèi)核資源,影響了處理速度。Cortex—M3和ARM7中斷控制器在功能和實現(xiàn)方式上的差異如表2所列。

3.1 處理器響應(yīng)單個異常

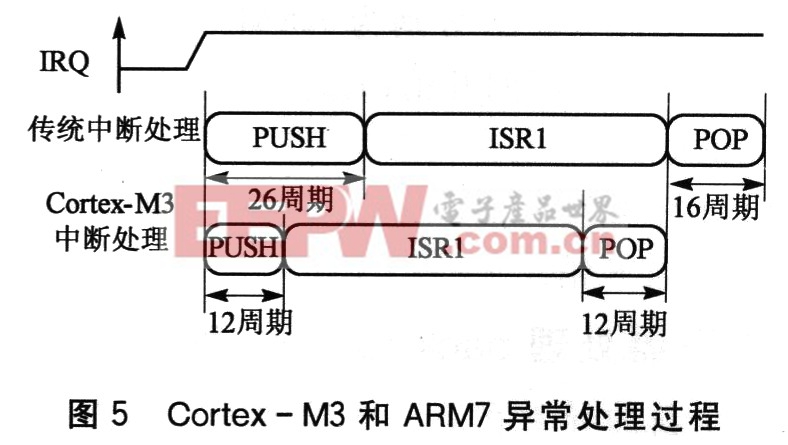

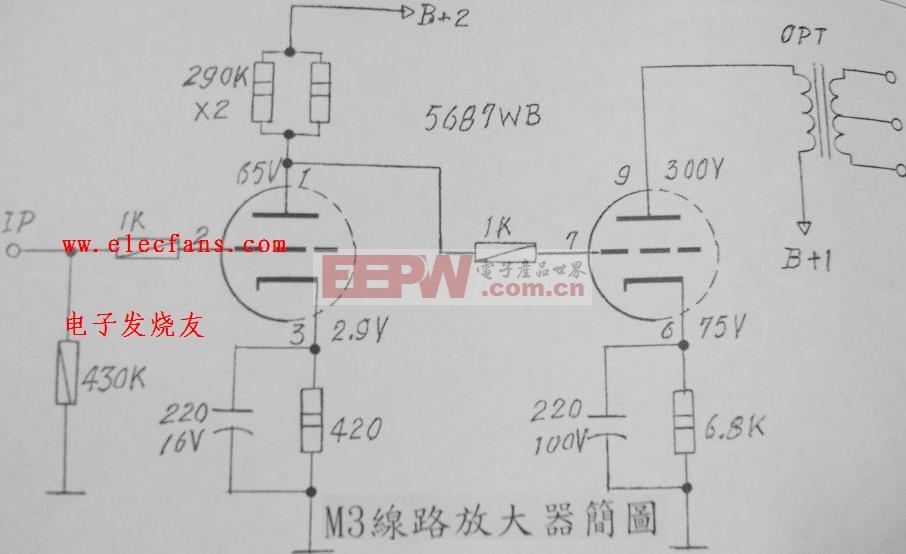

Cortex一M3和ARM7異常處理過程如圖5所示。

ARM7處理器的異常開銷:

其中,TARM7為ARM7處理異常的時間開銷;TARM2_PUSH和TARM7_POP為ARM7進(jìn)行壓棧和出棧的操作時間;TCoretx-M3為Cortex一M3處理異常的時間開銷;TM3_PUSH和TM3_POP為Cortex—M3進(jìn)行壓棧和出棧的操作時間。

評論