基于FPGA 的ARM 并行總線研究與仿真

WE 為ARM 輸入到FPGA 的寫使能信號.CS 為ARM 輸入到FPGA 的片選信號,FPGA 沒有被ARM 選中時必須輸出高阻態,以避免總線沖突.

2.2 FPGA 的雙向總線設計

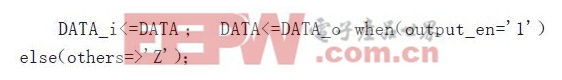

在FPGA 的并行總線設計中,如果頂層和底層的模塊都要用到雙向的IO 端口,則要遵守設計原則;否則不利于VHDL 程序的綜合.雙向IO 端口的設計原則是:只有頂層設計才能用INOUT類型的端口,在底層模塊中應把頂層的INOUT 端口轉化為獨立的IN(輸入).OUT(輸出)端口并加上方向控制端口.頂層設計的VHDL 代碼如下:

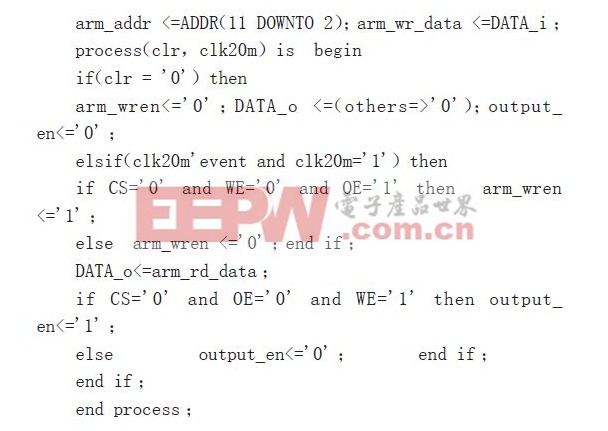

其中,DATA_i.DATA_o 和output_en 均為FPGA 內部的信號,在內部的各層次模塊中,通過這三個信號就可以進行單向的IO 控制.這樣,頂層設計中雙向的DATA 端口轉化為了內部單向的DATA_i(輸入).DATA_o(輸出)和output_en(輸出使能).在內部各模塊中,結合這三個信號以及ADDR.OE.WE.CS 等信號,則可方便地實現ARM 總線接口的功能.實現的VHDL 關鍵代碼如下:

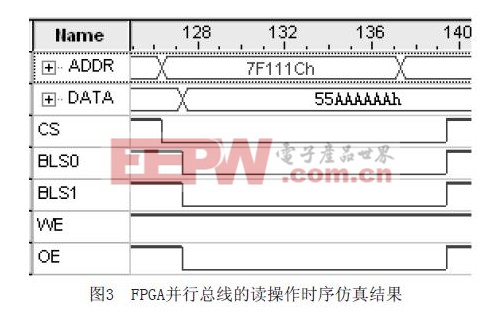

3 仿真結果分析

通過Quartus II 仿真工具,對FPGA 并行總線進行時序仿真;仿真結果如圖3 所示.根據ARM 并行總線的讀寫時序圖要求,從仿真結果可以看出FPGA 的總線接口設計滿足了設計的要求.由于選用的FPGA 器件內部帶有邏輯分析儀的功能模塊,通過Quartus II 軟件中的SignalTap II 邏輯分析工具,對FPGA的設計模塊進行在線測試,發現總線時序了滿足ARM 并行總線的要求,且工作穩定,從另一個角度驗證了設計和仿真結果的正確性.

4 結論

由于FPGA 技術和ARM 技術應用越來越廣泛,通過設計并行總線接口來實現兩者之間的數據交換,可以較容易地解決快速傳輸數據的需求,因此設計滿足系統要求的FPGA 并行總線顯得尤為重要.本文設計的FPGA 的ARM 外部并行總線接口,滿足了總線的時序要求,并在某航空機載雷達應答機中進行了應用,系統運行穩定,性能良好.以上的設計和仿真方法,對其他類似的設計也有一定的參考作用.

評論