基于AVR和FPGA數字式移相信號發生器的設計

1 引 言

移相信號發生器屬于信號源的一個重要組成部分,但傳統的模擬移相有許多不足,如移相輸出波形易受輸入波形的影響,移相角度與負載的大小和性質有關,移相精度不高,分辨率較低等。

而且,傳統的模擬移相不能實現任意波形的移相,這主要是因為傳統的模擬移相由移相電路的幅相特性所決定,對于方波、三角波、鋸齒波等非正弦信號各次諧波的相移、幅值衰減不一致,從而導致輸出波形發生畸變。目前利用DDS技術產生信號源的方法得到了廣泛的應用,但是專用DDS芯片由于采用特定的集成工藝,內部數字信號抖動很小,不可以輸出高質量的模擬信號。隨著現代電子技術的發展,特別是隨單片機和可編程技術的發展而興起的數字移相技術卻很好地解決了這一問題。在眾多的單片機之中,AVR 單片機是目前最新單片機系列之一,其突出的特點在于速度高、片內硬件資源豐富等。以FPGA為核心的PLD產品,是近幾年集成電路中發展最快的產品。采用FPGA芯片,可并行處理多項任務,其高速性能好(執行速度達到納秒級),純硬件系統的可靠性高。利用FPCA實現DDS能很好地解決專用DDS芯片的諸多缺點,他可以根據需要方便地實現各種比較復雜的調頻、調相和調幅功能,具有良好的實用性。

本文結合AVR系列單片機ATmega16和采用FPGACyclone器件實現DDS的一種數字式移相信號發生器設計新方案。該方案具有靈活可變的特點,更重要的是可以和其他功能模塊組合擴展為任意信號發生器。

2 系統總體方案設計及實現

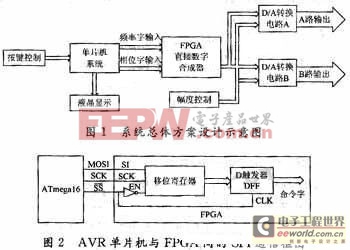

圖1是系統總體方案設計示意圖,他包括鍵盤按鍵控制部分,單片機系統部分,FPGA部分,以及幅度控制和D/A轉換電路。單片機采用ATmega16,他根據矩陣式鍵盤輸入給FPGA送出頻率控制字與相位控制字,用于設定輸出正弦波的頻率與相位。高速D/A轉換器用于正弦波的DA轉換,利用單片機的幅度控制字來控制他的參考電壓可以達到數字調幅的目的。FPGA構成DDS的核心部分,用于接收送來的頻率字與相位字,同時給DA轉換器輸出正弦波數據。采用字符型液晶1602A顯示屏實時顯示輸出的頻率與相位。

2.1 單片機與FPGA間的通信

ATmega16的同步串行接口允許在芯片和外設之間,或幾個AVR單片機之間,以與標準SPI接口協議兼容的方式進行高速的同步數據傳輸。本系統中,ATmega16只負責發送數據,不需要接收數據,故設置為主機工作模式。圖2為單片機與FPGA通過SPI通信的框圖。

2.2 數控移相信號發生器設計

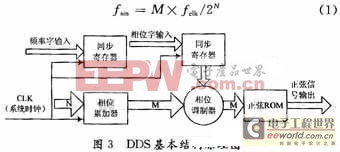

DDS的主要思想是從相位的概念出發合成所需的波形,他的基本原理框圖如圖3所示。他采用了相位累加振蕩方法的直接數字合成系統,把正弦波在相位上的精度定為N位,得分辨率為1/2N。用時鐘頻率fclk一次讀取數字相位圓周上各點作為地址,對出相應ROM中的正弦波的幅度值,然后經DAC重構正弦波。相位累計器的作用是讀取數字相位圓周上各點時可以每隔M個點讀一個數值,從而得到輸出正弦波頻率fsin為:

基于DDS的數字移相信號發生器是整個系統的設計核心部分,其電路模型圖如圖4所示。這部分完全是由VHDL語言設計,并在FPGA Cyclone器件上實現的。電路要求能輸出2路正弦信號,由2路10位D/A實現波形輸出。信號頻率能通過輸入的8位頻率控制字同步控制;其中一路作為參考信號,另一路是可移相的信號,可通過輸入的8位相位控制字控制。其中“FWORD”是8位頻率控制字,控制輸出波形信號的頻移量;“PWORD”是8位相移控制字,控制輸出波形的相移量;ADDER32B及AD-DER10B分別為32位和10位加法器;SIN_ROM是存放波形數據的ROM,10位數據線,10位地址線(數據和地址線最大可以到32位),其中正弦波數據文件是后綴為mif的文件,可由C程序直接生成。REG32B和REG10B分別是32位和10位寄存器;POUT和FOUT為8位輸出,可以分別與兩個高速D/A連接,輸出參考信號和可移相波形信號。

評論