基于AMBA-AHB總線的SDRAM控制器的計方案

SDRAM上電后必須按一種確定的方式初始化。在上電穩定后100 μs時間內存儲器不接受除NOP以外的任何命令。當100 μs過后,通過控制器向SDRAM所有bank 發出預充電(Precharge)命令[8],使SDRAM 所有bank進入待機狀態。之后,要對SDRAM 連續執行兩個自動刷新操作,使SDRAM 芯片內部的刷新及計數器進入正常運行狀態。兩個刷新周期完畢之后,開始對SDRAM 的模式寄存器(Mode Register)進行操作,模式寄存器用來決定SDRAM將以何種工作模式工作。整個初始化過程如圖2所示。

3 SDRAM 控制器與AMBA-AHB 總線的關系

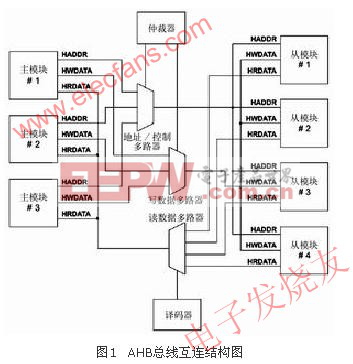

本設計基于AMBA-AHB總線的slave模塊,SDRAM控制器處在片內AHB 總線與片外存儲設備之間,作為一個從機掛在AHB總線上。它一邊需要通過AHB總線接口模塊與AHB總線通信,因此必須符合AHB總線標準;另一邊又需要給外部存儲設備提供控制信號,以實現對外部存儲設備的讀寫操作。控制器接收來自總線主設備的符合AMBA-AHB 總線規范的數據傳輸請求,產生正確的讀寫控制信號給SDRAM 存儲器,以完成總線的數據傳輸請求。

AMBA 2.0總線為嵌入式微控制器定義了一套片上總線標準,因此本設計是獨立設計的基于該規范的外圍IP.

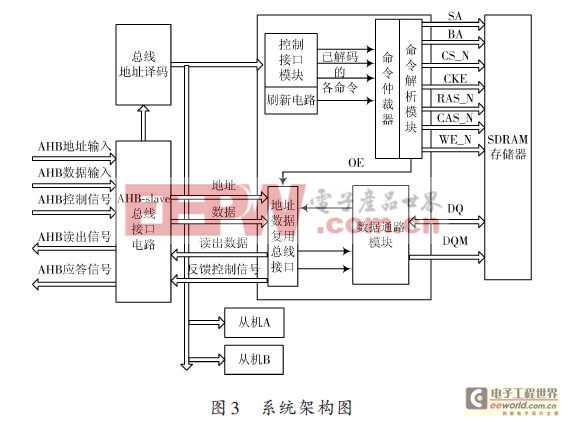

4 SDRAM 控制器系統設計架構

SDRAM 控制器與AHB 總線接口在整個系統中的連接關系如圖3所示。

4.1 AHB-slave總線接口電路

AHB-slave總線接口電路用來實現SDRAM 控制邏輯與AHB-master之間的信號傳輸。

按照AMBA 總線規范要求,AHB 總線從設備(slave)在總線時鐘上升沿,HREADY信號(由從設備發出)為高的情況下,必須鎖存來自AHB總線的總線控制信號、數據信號、地址信號等,以供內部譯碼模塊以及其他各模塊使用。

評論