基于AMBA-AHB總線的SDRAM控制器的計方案

0 引言

隨著大規模集成電路和高速、低功耗、高密度存儲技術的發展,SDRAM動態存儲器因容量大、速度快、價格低廉等優點,現已成為PC內存的主流。然而SDRAM存儲器內部控制邏輯十分復雜,時序要求也非常嚴格,因此需要設計專門的SDRAM 控制器來實現系統對SDRAM的訪問。

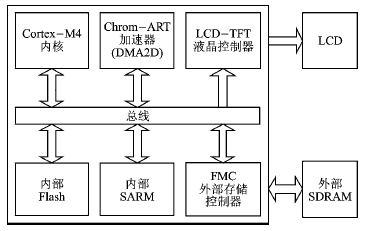

存儲控制器是嵌入式微處理器中AMBA-AHB總線與片外存儲設備之間的接口,完成總線主設備(CPU或DMA)與片外存儲設備(SDRAM或SRAM)的數據傳輸,其功能與性能決定著嵌入式微處理器所支持的外部存儲器的類型以及外部存儲器的訪問速度,進而決定著整個嵌入式系統的處理速度。AMBA總線規范成為嵌入了式微處理器內片上總線的標準,設計基于AMBA總線標準,支持嵌入式系統常用存儲器類型的存儲控制器IP具有非常大的現實意義。

1 AMBA 總線簡介

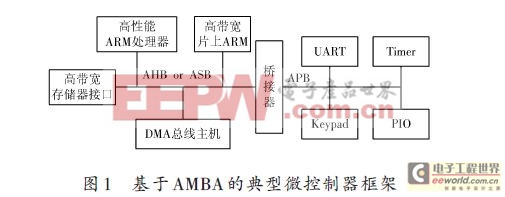

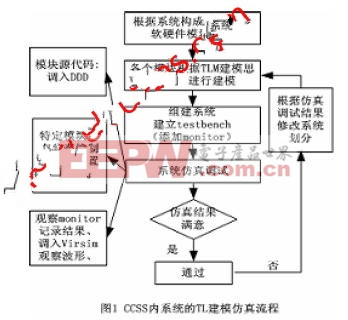

典型的基于AMBA總線的微控制器架構如圖1所示。

它包含一個作為系統骨架的AHB(Advanced High-Performance Bus)或ASB總線,可實現CPU或DMA模塊與片外存儲器之間的大量數據通信,以獲得大的帶寬。

另外,在這條高性能總線上還有一個橋接器以連接低帶寬的APB,而在APB上連接著大多數的系統外設。用戶可以各自獨立設計基于這個規范的微處理器以及外圍IP,提高了系統的開發效率及模塊的可重用型[6].

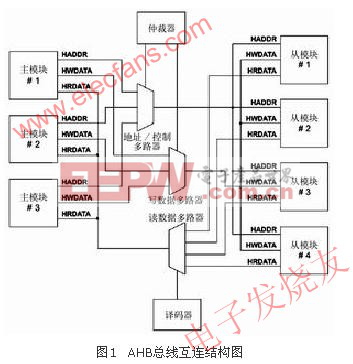

其中,AHB 總線是一種支持多總線主機的高性能總線,用于高性能、高時鐘頻率的系統,它保證了處理器與片外存儲器的有效連接。一個完整的AHB傳輸過程可以分為地址傳輸階段和數據傳輸階段,地址傳輸階段傳輸地址和控制信號,而數據傳輸階段傳輸的是讀寫數據和響應信號。AHB 總線支持流水線傳輸,也就是說在前一個數據傳輸階段可以同時進行下一個地址傳輸階段,前后不同的傳輸階段可以重疊起來以提高系統的數據處理速度。

2 SDRAM 工作原理

SDRAM 是一種高速高容量同步動態存儲器,相比于SRAM 等靜態存儲器具有容量大、速度快、價格低廉等優點,成為圖像處理中常用的數據存儲器。但因SDRAM存儲結構的特殊性,需要對SDRAM不斷進行預充電、刷新等操作以保持數據不丟失。SDRAM 內部的操作是通過總線命令實現的,命令由RASN、CASN 和WEN信號聯合產生,如表1所示(H表示高電平,L表示低電平)。

評論