基于FPGA的DDR3控制器設計

摘要 介紹了DDR3 SDRAM的技術特點、工作原理,以及控制器的構成。利用Xilinx公司的MIG軟件工具在Virtex-6系列FPGA芯片上,實現了控制器的設計方法,并給出了ISim仿真驗證結果,驗證了該設計方案的可行性。

本文引用地址:http://www.104case.com/article/201609/303621.htmDDR3 SDRAM是第三代雙倍數據速率動態同步隨機存儲器的簡稱。是SDRAM內存產品家族中的一員。DDR3內存模組是采用多顆DDR3 SDRAM,并根據JEDEC的相關內存模組設計標準而制作。DDR3SDRAM有如下技術特點:(1)DDR3新增了重置(RESET)功能,并為此新功能設置了管腳,當RESET命令有效時,DDR3將終止所有操作,此時處于活動量最少的狀態,以降低功耗。(2)DDR3新增ZQ校準功能,ZQ也是一個新的管腳,這個引腳通過一個命令集及片上校準引擎(On—Die Calihration Engine,ODCE)自動校驗數據輸出驅動器導通電阻與ODT的終結電阻值。(3)在DDR3系統中,將參考電壓分成兩個:一個是為地址和控制總線提供服務的VREFC,另一個是為數據總線提供服務的VREFDQ,兩個不同的參考電壓為DDR3提供更好的抗噪能力。(4)在DDR3系統中,控制器和存儲器是一一對應的,由此便可大幅減輕地址、控制、數據信號的總線負擔,提供了信號的完整性。這是DDR3和DDR2的一個關鍵區別。對單個Rank的模組,控制器和內存是點對點(Point to Point)的連接關系,對雙Rank的模組,控制器和內存是點對雙點(Point to 2Points)的連接關系。(5)DDR3存儲器模塊的地址、命令、控制信號和時鐘采用了“Fly—by”的拓撲結構,大幅減輕了地址、命令、控制和數據總線的負載,提高了信號的完整性。

1 DDR3 SDRAM工作原理

系統上電后,在DDR3 SDRAM進行正常讀寫操作前,必須按照規定步驟完成初始化操作,然后才能進入空閑的狀態,等待控制器的訪問。初始化操作過程中主要完成對模式寄存器的配置工作,DDR3芯片上有4個模式寄存器,通過模式寄存器的配置,可完成比如突發長度、讀取突發種類、CAS長度、測試模式、DLL復位、輸出驅動能力等的設置。

DDR3 SDRAM的工作狀態轉換是通過指令來實現的,主要通過CS#(片選信號)、RAS#(行選通信號)、CAS#(列選通信號)、WE#(讀寫控制信號)之間的組合狀態實現,DDR3 SDRAM支持的命令主要有:

(1)預充電命令。作用是關閉特定Bank中打開的行或者所有Bank中打開的行,SDRAM尋址具有較強的獨占性。對于第一次的讀寫,只需用激活命令打開此行即可,而對于當前行仍處于打開狀態,要對新一行進行讀寫,此時就要關閉當前行,此命令就是預充電命令。

(2)刷新命令。SDRAM單元有個缺點就是用電容存儲數據。但由于漏電流的存在,數據不能長時間存在存儲單元中,需要周期性的刷新來保持數據,所以在SDRAM進行存儲工作時,必須進行刷新操作。刷新間隔和存儲芯片的溫度有關,刷新方式分為自刷新(SREF)和自動刷新(AREF)。自刷新用于正常模式下,而自動刷新用于低功耗情況下。

(3)激活命令。用于激活所要進行讀或者寫操作的Bank、行和列。在讀或者寫命令到達DDR3 SDRAM的行之前,要先對要讀或寫操作的行用激活命令進行激活。與激活命令一起發送的地址位用于尋找進行操作的Bank和行,與讀或寫命令一起發送的地址位用于尋找進行操作的起始列單元。

(4)讀命令。用于對一個已激活的行進行讀操作。在讀操作完成之后,被訪問的行依然處于打開狀態,直到被預充電命令關閉。BA0~BA2用來選擇Bank的地址,A0~Ai提供的輸入地址用于選擇開始列地址,讀命令操作如圖1所示。

(5)寫命令。用于啟動一個突發的存儲器寫操作,由FPGA向DDR3 SDRAM中寫入數據。BA0~BA2用于選擇Bank的地址,A0~Ai提供的輸入地址用于選擇開始列地址由FPGA將數據寫入DDR3 SDRAM中。寫命令操作如圖2所示。

DDR3芯片內部控制器中有8個Bank處于開放的狀態,Bank開放的順序由控制器發出的命令決定。若8個Bank均處于開放狀態,但還有數據要進入Bank,則最后開放的Bank將被關閉,以打開一個新的Bank。在自刷新時,所有Bank都會被關閉,一旦有預充電命令,Bank就會開放。

2 DDR3 SDRAM控制器設計方案

設計采用Xilinx公司提供的DDR3 SDRAM控制器IP核。采用此方案的好處是縮短開發周期、簡化系統設計。設計者只需在Xilinx公司提供的MIG3.92軟件工具界面上選擇FPGA及DDR3 SDRAM芯片型號、總線寬度、速度級別,設置突發長度、CAS延遲、引腳分配等參數,即可生成DDR3 SDRAM控制器。FPGA芯片采用Xilinx公司的Virtex-6系列XC6VLX240T-1FFG1759C型號,DDR3 SDRAM芯片采用鎂光公司的MT8JSF25664HZ-1C4D1,該內存芯片行地址寬度為15位。列地址寬度為10位,Bank地址位寬為3位,總容量為2 GB。設置突發長度為8位,數據寬度為64位,速度級別為-2,時鐘頻率為400 MHz。

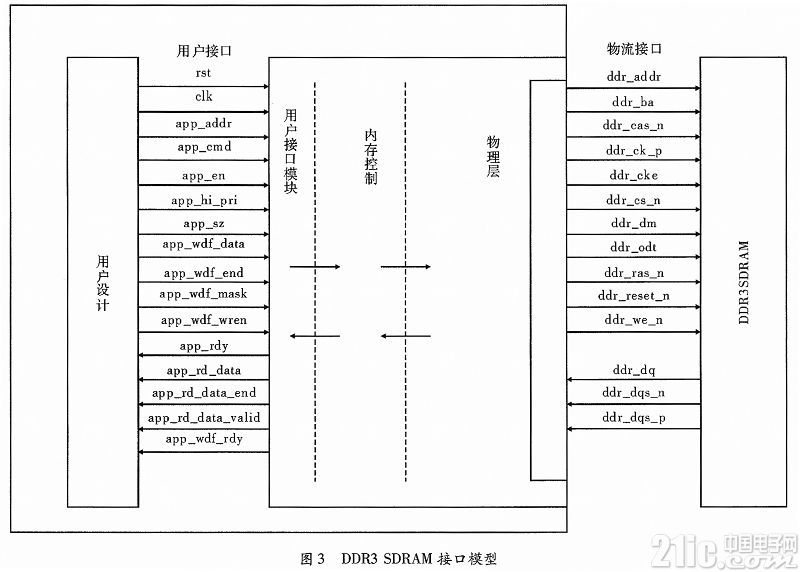

DDR3 SDRAM控制器的主要功能是完成對DDR3SDRAM的初始化,將DDR3 SDRAM復雜的讀寫時序轉化成用戶簡單的讀寫時序,將DDR3 SDRAM接口的雙時鐘數據轉化成用戶的單時鐘數據,并發送周期性的刷新命令來維持DDR3 SDRAM中的數據。控制器主要分為傳輸層和物理層,傳輸層負責接收上層用戶邏輯的訪存請求,并將這些請求轉換成DDR3SDRAM所需的時序發送給物理層。物理層負責將控制和地址信號按照DDR3 SDRAM需要的時序發送給存儲芯片,同時在傳輸層和存儲芯片之間創建地址通路和數據通路,捕獲DDR3 SDRAM發出的數據,通過輸入輸出緩存發送DDR3 SDRAM所有的控制信號、地址信號以及數據信號,同時保證指令與地址,數據的同步,DDR3 SDRAM接口模型如圖3所示。

DDR3 SDRAM內存控制器的設計必須滿足兩大基本要求:(1)所設計的控制器要實現對內存模組的管理,完成CPU的訪存要求。(2)需盡可能提高訪問內存的速度和帶寬,這是衡量內存控制器性能的重要指標,同時還需考慮內存的兼容性和成本問題。

3 實驗結果

為驗證DDR3控制器IP核的正確性,對MIG生成的測試模塊在ISE14.2環境下進行功能仿真驗證,該模塊可以對DDR3存儲器進行一系列操作,并對寫入和讀出的數據進行比較,從而驗證控制器的正確性。仿真結果如圖4所示,phy_init_done的值為1,說明初始化完成。當app_cmd=000時,表示當前進行寫操作,只有同時app_en=1和app_rdy=1,app_ addr才能寫入成功。當app_cmd=001時,表示當前操作為讀操作,可通過rror這一比較信號驗證控制器是否正確。從仿真結果可看出,比較信號error始終為低電平,說明寫入和讀出的數據是一致的。

4 結束語

通過對DDR3的技術特點和工作原理進行分析,將DDR3控制器的從層次上分為傳輸層和物理層,然后給出了DDR3 SDRAM控制器的設計方法,將控制器在Xilinx公司的Virtex-6系列FPGA芯片上實現,通過ISim軟件仿真結果,證明了設計的可行性和正確性,以及IP核設計的DDR3控制器具有較好的適應性和靈活性,縮短了系統開發周期、降低了系統開發成本。

評論