基于S3C2410A多個AD7656-1組成菊花鏈的數據采集系統

在變電站自動化系統中,常需要對多個三相電壓電流信號進行數據采集和處理(如電能質量實時監控),這時需要實現對多路信號的同時、快速的數據采集。美國模擬器件公司(ADD的AD7656-1是一款16位6通道的模/數轉換芯片,內部含有6個獨立的A/D轉換器,可同時進行A/D轉換,具有轉換精度高、速度快、功耗低、輸入模擬信號幅度大、信噪比高等優點,其突出特點是可通過多個AD7656-1級聯形成菊花鏈實現多個通道同時進行數據采集,并通過一個或多個串口發送數據給主控處理器。以S3C2410A為主控處理器,多個AD7656-1組成菊花鏈實現多通道、高精度的ADC,在很大程度上可提高數據采集系統的信號采集和處理能力,具有較好的應用前景。

1 AD7656-1的特點

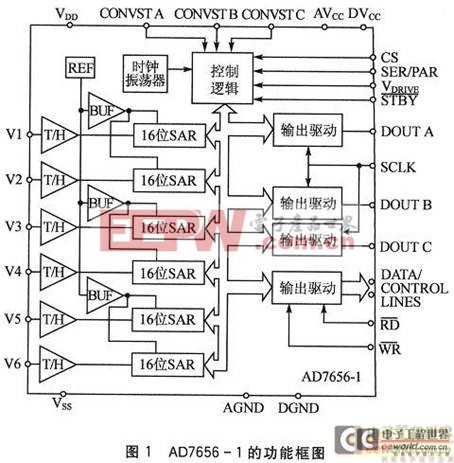

圖1為AD7656-1的內部功能框圖。其主要特性為:

6個獨立的16位逐次逼近(SAR)型模數轉換器。

可通過引腳或軟件方式設定輸入信號的電壓范圍(±10 V,±5 V)。

最高吞吐率為250 ksps。

寬帶寬輸入高信噪比:輸入頻率為10 kHz時的信噪比(SNR)為88 db。

帶有片上2.5 V基準電壓源和基準緩沖器。

低功耗,5 V供電時在250 kSPS下功耗僅為140 mW。

支持并行、串行及菊花鏈接口模式。

高速串行接口,兼容SPI/QSPI/MICROWIRE/DSP。

采用iCMOS制造工藝,64引腳的LQFP封裝。

應用領域:輸電線路監測系統、儀器儀表和控制系統、多軸定位系統。

2 AD7656-1菊花鏈工作原理及其配置

2.1 AD7656-1菊花鏈工作原理

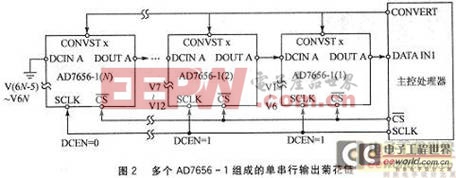

AD7656-1有2種接口模式:串行接口模式和并行接口模式。在數據轉換時,3個轉換信號CONVSTA/B/C用來控制每對或每4個或每6個ADC同時采樣。如果將3個CONVST引腳連接在一起接收同一個采樣啟動信號,就可使6個ADC同時進行采樣,此時再將多個AD7656-1級聯就可以形成菊花鏈,實現6N(N=2,3,…,8)個ADC通道同時采樣,如圖2所示。在CONVSTX的上升沿,ADC被置為保持模式,轉換開始。CON-VSTX的上升沿過后,BUSY信號變為高電平表明轉換正在進行,3μs后BUSY信號返回低電平表明轉換結束。在BUSY信號的下降沿,ADC回到跟蹤模式。數據可以通過1~3個串行接口從輸出寄存器讀出,并由主控處理器接收并存儲。AD7656-1采用同步串行接口(SPI)發送數據時,每發送一個比特位數據就要花去一個單位的SCLK脈沖的時間,發送完6個通道的16位數據就要花去96個SCLK脈沖。菊花鏈中多個AD7656-1通過數據接力傳遞的方式把數據依次發送給主控處理器,通過采用多個串行接口發送數據可減少發送時間,提高菊花鏈的數據傳遞效率。AD7656-1串行數據輸出接口及其對應的通道數據關系和發送所需的SCLK脈沖個數關系如表1所列。

2.2 AD7656-1菊花鏈的配置

AD7656-1要工作在菊花鏈方式,其數據輸出必須設置為串口模式,且在串口模式下,AD7656-1必須配置成硬件模式。所謂的硬件模式是通過對器件引腳的固定連接,確定AD7656-1 芯片唯一的工作方式,此時AD7656-1也不能配置成軟件工作模式了。AD7656-1菊花鏈配置的主要原則如下:

①在多片級聯的AD76561中,位于級聯最遠端的芯片不能配置為菊花鏈工作模式,即其DCEN引腳置低電平(數字地);但其下流數據鏈的每片AD7656-1必須配置為菊花鏈工作模式,即DCEN引腳都要置邏輯高電平(VDRIVE)。

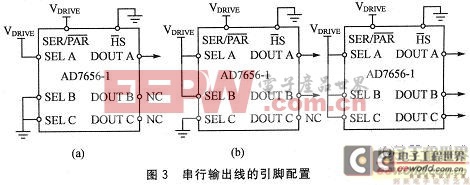

②SEL A、SEL B、SEL C對應使能DOUT A、DOUT B、DOUT C串口輸出口。要選用DOUT X串行輸出口,就置對應的SEL X為邏輯高電平,其余不用的SEL引腳必須置邏輯低電平。圖3(a)、(b)、(c)為1~3個串行輸出口的引腳配置。(圖中“NC”表示未連接)

③菊花鏈中的每片AD7656-1的串行數據輸入/輸出(DCIN X/DOUT X)必須遵循同一配置,即有幾個DCIN輸入就有幾個DOUT輸出。

評論