三十二通道掃描PCI數據采集模塊的設計方案

引言

數據采集模塊是自動測試系統中的主要功能模塊之一,在光譜分析、醫療成像等領域,通常需要組建多時基、多通道虛擬儀器系統,有些領域要求輸入信號頻率并不高,從幾赫茲到幾百赫茲。對于不同頻率范圍的信號,通常要求的采樣率也不同。有時為了配合信號處理算法,甚至要求采樣率可以在一定范圍內隨意設定。這些應用通常要求多個通道循環掃描采集,甚至是差分單端方式可選擇的輸入,對于不同的應用還要求增益的可變性。針對這些要求,本文介紹了一種三十二通道掃描數據采集模塊的設計方案。該方案最高采樣率為200KSa/s,存儲深度IM×16bit ,垂直分辨率16bit,增益可編程為1、2、5、10、100五個等級的PCI數據采集模塊的設計與實現。

總體設計方案的確定

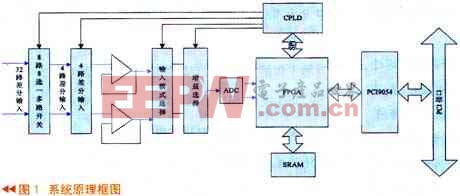

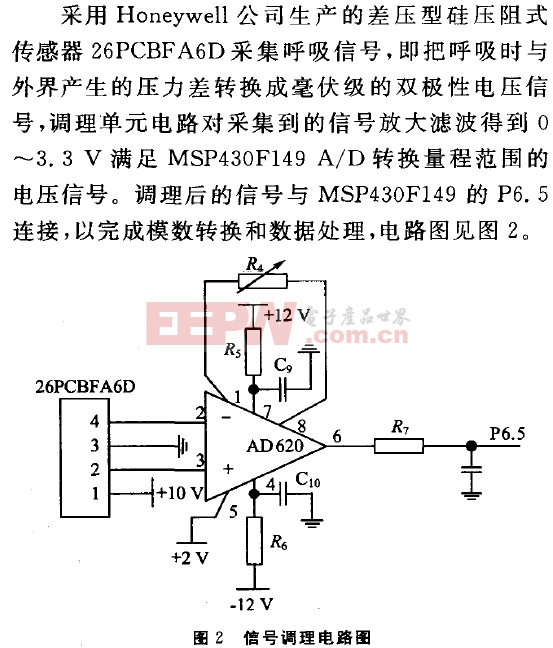

根據上述系統的技術指標,本設計硬件電路主要包括信號調理電路、信號輸入方式選擇電路、程控增益電路、A/D轉換、數據存儲、觸發控制以及PCI接口幾個部分。三十二個通道的模擬信號經過信號調理電路使信號的帶寬、峰值和偏置電壓等達到ADC的輸入信號要求后,經過單端變差分的轉換(前端也可以是直接輸入的三十二路差分信號),通過多路開關選擇輸入的多種方式,再通過兩級可編程增益儀用放大器進行增益的控制,然后進入ADC把模擬信號轉換成相應的數字信號。邏輯控制單元在接收到采集命令后,根據相應的觸發方式啟動ADC進行采樣,采樣得到的數據通過FPGA內部FIFO直接發送到上位機處理或者存儲到高速的靜態RAM中以便歷史顯示。三十二個通道共享RAM最大的采樣速率是200KSa/s,那么連續采樣存儲時間最大可以達到4s。上位機通過32位的數據總線,采用查詢、中斷或者DMA方式將采集的數據讀取到內存中進行后期的數據處理和分析。基本結構如圖1所示。

信號調理電路設計

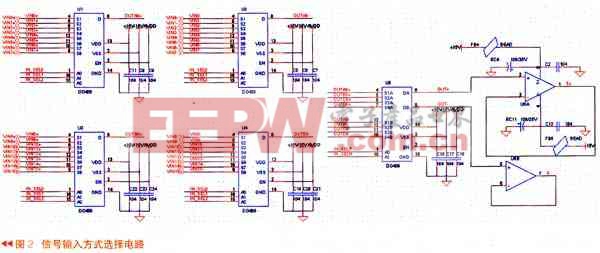

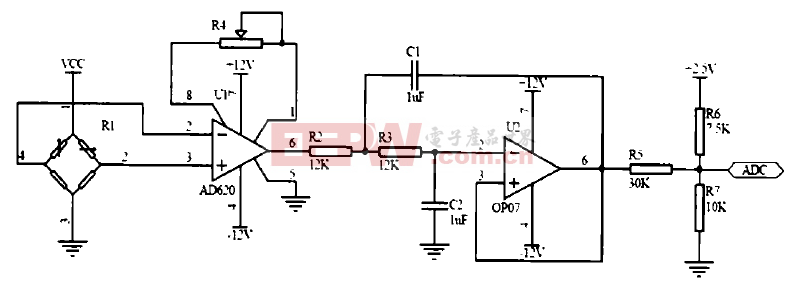

本設計信號調理電路包括輸入方式選擇電路和增益選擇電路。將經過前端模塊調理電路變成的三十二路差分信號(或者直接從接口輸入的三十二路差分信號)通過低導通阻抗、低泄漏電流、帶過壓保護的多路模擬開關切換成一路差分通道,再通過普通運放構成的電壓跟隨器進行阻抗變換,避免后級的多路開關的導通阻抗影響前級電路。多路開關選擇DG408,它是八選一多路開關,具有較低的導通阻抗和低功耗、低泄漏電流。通過八個DG408把三十二通道的差分輸入變換成四通道的差分輸入,再通過一個DG409(4路差分開關),將輸入信號變成一路差分輸入,然后再經過一個DG409選擇信號的輸入方式,通過這樣的電路能實現四種輸入方式:零輸入、單端正極輸入、單端負極輸入和差分輸入,電路如圖2所示。

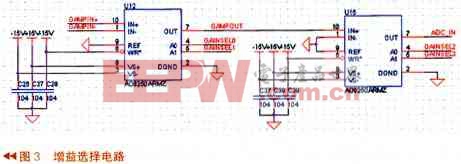

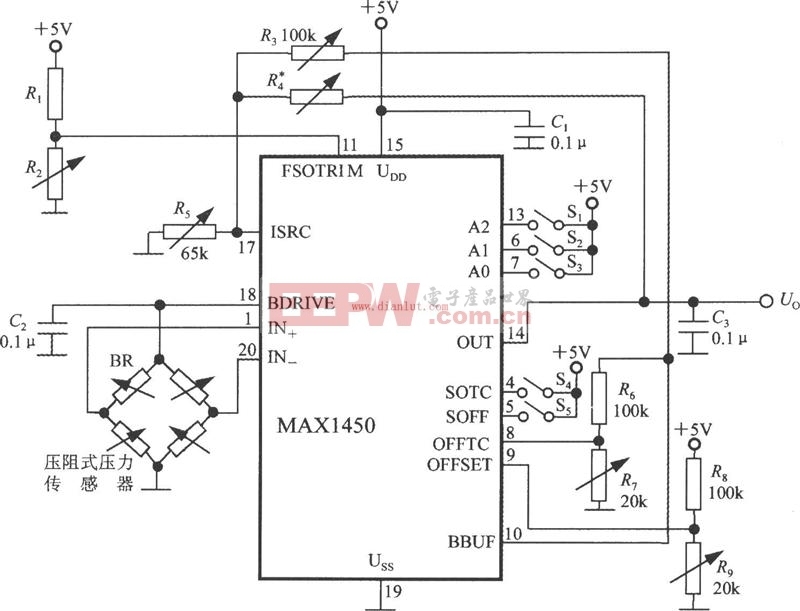

選擇一種輸入方式后,經過兩級可編程增益儀表放大器AD8250,可以實現增益值可選1、2、5、10、100五個等級。AD8250具有較寬工作電壓范圍,可以工作在±5V~±15V;輸入阻抗可以達到G?級別,有效防止了消耗的衰減;單個AD8250有1、2、5、10四個增益選擇,在G=10的時候仍具有最小98dB的高共模抑制比和低增益漂移。AD8250有兩個增益控制端A0、A1,通過寫這兩個位選擇增益值,通過WR可以鎖存狀態值,從而穩定保持在該增益值上。本設計通過在FPGA內部內嵌32bit NIOSII軟核處理器,NIOSII通過SPI總線傳送數據給CPLD然后控制選擇信號的輸入方式和寫AD8250增益控制位。增益選擇電路如圖3所示。

數據采集與控制電路設計

A/D轉換器是數據采集系統的核心,對A/D器件的選擇往往影響到整個系統的性能指標,甚至可能需要重新設計電路。為了實現三十二通道掃描采樣,本設計采用多路提取技術,把三十二路差分輸入信號經過兩級多路開關提取出一路差分信號,再通過增益變換電路將差分信號變成單端模擬信號輸入到ADC中進行采樣,通過FPGA控制CPLD定時掃描的方式實現三十二通道輪流采樣。本設計選擇的A/D轉換器是ADI公司的AD7612,它具有-路雙極性的高阻抗輸入,采樣速率為750KSa/s,具有可選擇的并行或者串行的輸出接口,容易與其他器件連接。AD7612內部集成了采樣的時鐘電路,具有可選擇的內部2.5V參考電壓或者外部用戶自己提供的參考。AD7612有四個差分輸入范圍和三個差分輸入模式,不同的模式對應不同的特點。Warp模式具有最快的吞吐率,正常模式具有最快的異步吞吐率,脈沖模式可以實現吞吐率和功耗的線性映射。根據技術要求本設計選用正常模式,采用并行16位數據的輸出方式和FPGA直接接口。根據AD7656的內部時序將采集的數據并行輸出到數據緩沖池和SRAM中。

本設計數字控制部分由FPGA和外擴的CPLD共同合作完成。FPGA內部嵌入一個NIOSII軟核,負責數據采集、數據傳輸和輸入方式以及增益的選擇控制。下面詳細分析這三個數字控制電路的實現方法。

信號輸入方式和增益選擇控制邏輯的實現

FPGA和CPLD之間通過SPI同步串行總線通信。通過在FPGA內部構建一個5bit地址總線,5bit數據線的RAM塊用來存儲三十二個通道碼。再構建一個8bit地址線,8bit數據線的RAM塊用來存儲信號的輸入方式和增益值。8bit數據的前兩位是輸入方式的選擇碼,后六位是增益選擇碼。在送通道碼之前只送一次輸入方式和增益值碼,直到下一次需要改變的時候再送。在CPLD中構建一個二選一的開關和64bit的串并轉換把通道碼或者輸入方式選擇碼和增益選擇碼送到相應的引腳。從而實現信號順序掃描和點名掃描以及相應的輸入方式和增益選擇控制邏輯的實現。

數據采集和傳輸控制邏輯的實現

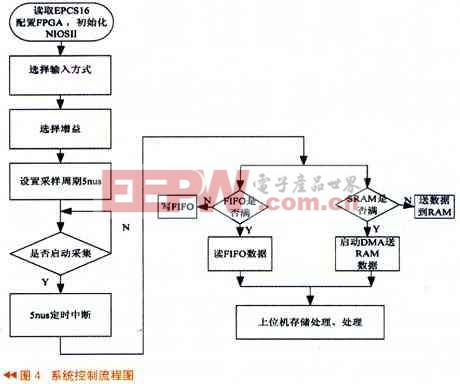

為了便于控制,本設計在FPGA內部嵌入一個NIOSII軟核處理器,NIOSII處理器通過 Avalon總線與外設通信,根據設計的要求,在NIOSII處理器中定制帶中斷的定時器、DMA控制器、SPI控制器和PIO控制器。由于設計要求最高采樣率是200KSa/s,而AD7612從啟動采樣到得到穩定的數據時間是1.5μs ,所以通過設定定時器最短的時間5μs(200KSa/s任意設定,可以通過實時設置定時器的值來完成)來實現。每隔5μs,定時器計數到0,產生一次IRQ中斷,在中斷服務程序中執行如下操作:

讀取ADC采集的結果;

是否需要改變輸入方式和增益,如果需要,送下一個值;

送下一個通道碼;

判斷ADC緩沖池( 30K×16bit FIFO)是否已滿,如果滿則把讀取的數據扔掉,否則把數據送到FIFO中;

在送數據到FIFO的同時,也需要復制數據到RAM中。RAM數據的存儲需要在FPGA中設計一個20bit的向上增加的地址計數器來制定數據的存儲位置,也要設計一個數據比較器,當計數器計滿時,跟數據比較器預設的值相等,產生一個電平,將RAM的數據通道斷開,同時告訴NIOSII啟動DMA控制器,在PCI9054的本地總線和RAM之間建立一個DMA通道,把數據取走。圖4是系統控制流程圖。

PCI接口控制時序

本設計采用PCI總線作為數據總線連接采集模塊和上位機進行通信,用以實現數據的分析處理和歷史顯示等功能。

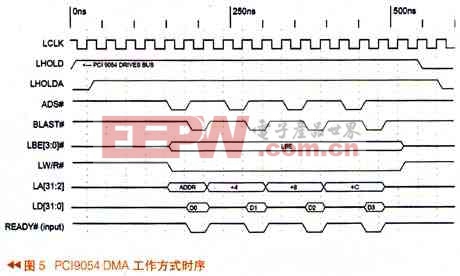

由于本文設計的采集模塊需要工作在連續采集的系統中,所以當存儲器存滿之后,需要快速地輸出通道并將數據通過PCI接口傳輸出去,本設計采用DMA的方式傳輸數據,這樣做既可以不占用CPU資源,又能實現快速的數據傳輸。基于以上原因本設計選用PCI接口芯片PCI9054作為總線控制器和上位機通信。該芯片符合PCI2.2總線規范,支持低成本從屬適配器,PCI時鐘為0~33MHz,基本可達到60Mbyte/s的平均傳輸速率。

FPGA按照PCI9054的讀寫時序設計讀寫控制邏輯,接收上位機傳來的命令,對電路進行相應的設置后,啟動ADC采集數據,然后將采集的數據送到ADC緩沖FIFO中(或者控制將存儲在RAM中的數據),當FIFO滿后(或者RAM滿后)通過相應的傳輸方式將數據發送到PCI9054的本地數據線上,并將地址譯碼作為局部器件的地址片選,從而實現對PCI總線的局部器件的訪問。PCI9054從模式的局部總線包括局部時鐘線LCLK,數據線LD[31..0],地址線LA[31..2],控制狀態線ADS#,LBE[3..0]#,BLAST#,LW/R#,READY#和仲裁線LHOLD和LHOLDA。本設計使用了16位的本地數據總線和24位地址總線進行數據傳送和地址譯碼控制。PCI9054 DMA方式工作時序圖如圖5所示。

結論

通過詳細分析各種數據指標,本文所設計的PCI數據采集模塊,充分考慮設計中各種影響信號質量的因素,包括噪聲的抑制和信號衰減等。合理的設計保證了PCB板設計方面的電磁兼容性和信號回路方面的要求,同時綜合考慮各種方案,減小了PCB板的尺寸,減少了設計成本。通過FPGA內嵌NIOSII和擴展的CPLD可靠地實現了三十二個通道不同輸入方式、增益改變、順序掃描或者點名掃描的要求,通過定時中斷實現最高實時采樣率200KSa/s和低于200KSa/s時任意采樣率的設置指標。通過選用高精度的ADC實現了設計對16bit分辨率的需求,合理的元件選擇保證了檢測信號的幅值范圍為±100mV、±1V、±10V的各種量程需求。通過真實的硬件測試,各項指標均得到滿足。本文設計的PCI掃描采集模塊適用于最多三十二通道掃描采集的場合,同時根據設計思路可以擴展更多輸入通道和更高采樣速度和分辨率的采集模塊。

評論