模數轉換器時鐘優化:測試工程觀點

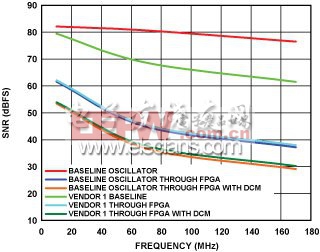

圖18. FPGA門驅動電路影響AD9446-80的性能

選擇最佳的時鐘驅動器是困難的。表2給出了市售的多個驅動器門所增加抖動的大致比較結果。表格下方給出的建議有助于獲得優良的ADC性能。

表2. 時鐘驅動器門及其增加的抖動

| 邏輯系列 | 注釋 |

FPGA | 33 ps~50 ps(僅包括驅動器門,未包括DLL/PLL內部的門)1 |

74LS00 | 4.94 ps2 |

74HCT00 | 2.2 ps2 |

74ACT00 | 0.99 ps2 |

MC100EL16 PECL | 0.7 ps2 |

AD951x系列 | 0.22 ps2 |

NBSG16,ECL擺幅減少(0.4V) | 0.2 ps2 |

ADCLK9xx,ECL時鐘驅動器系列 | 0.1 ps2 |

1制造商的說明書

2基于ADC SNR的下降換算的值

評論