電腦鍵盤工作原理

輔助設備(指 鍵盤) 檢查 時鐘線 ,如果時低電平,禁止發送數據

The auxiliary device checks the 'data' line. If the line is inactive, the controller receives data from the system.

設備檢查數據線,如果是 低電平,那么控制器從系統接收數據

The auxiliary device checks the 'clock' line during the transmission at intervals not exceeding 100 microseconds. If the device finds the system holding the 'clock' line inactive, the transmission is terminated. The system can terminate transmission anytime during the first 10 clock cycles.

設備在傳輸過程中 檢查 時鐘 線 間隔不超過100us。 如果設備發現 主機系統 將電平拉低,就終止傳輸。 在傳輸過程的前10個時鐘周期的任何時候,主機系統可以中止傳輸。

A final check for terminated transmission is performed at least 5 microseconds after the 10th clock.

終止傳輸的最后一個檢查 要持續至少5us

The system can hold the 'clock' signal inactive to inhibit the next transmission.

系統拉低時鐘線,將禁止下一次傳輸

The system can set the 'data' line inactive if it has a byte to transmit to the device. The 'data' line is set inactive when the start bit (always 0) is placed on the 'data' line.

系統如果有一個字節要傳輸給設備,可以拉低數據線。當開始位(總是0)放置到數據線時,數據線被拉低。

The system raises the 'clock' line to allow the next transmission.

系統拉高時鐘將允許下一次傳輸

Host-to-Device主機到設備的通信

First of all, the PS/2 device always generates the clock signal.

首先,PS/2設備總是產生時鐘信號

If the host wants to send data, it must first put the Clock and Data lines in a "Request-to-send" state as follows:

如果主機想發送數據,它必須先將時鐘線和數據線設置成"Request-to-send"狀態:

1) Inhibit communication by pulling Clock low for at least 100 microseconds.

拉低時鐘線至少100us來禁止通信

2) Apply "Request-to-send" by pulling Data low, then release Clock.

拉低數據線,請求 "Request-to-send", 然后釋放時鐘 .

The device should check for this state at intervals not to exceed 10 milliseconds.

設備應該在不超過10ms(注意,是毫秒)的間隔內就要檢查一次這個狀態。

When the device detects this state, it will begin generating Clock signals and clock in eight data bits and one stop bit.

當設備檢測到這個狀態,它將開始產生時鐘信號,

The host changes the Data line only when the Clock line is low, and data is read by the device when Clock is high.

只有當時鐘線 為低的時候,主機才可以改變數據線(也就是將數據寫入到數據線)。數據將在時鐘為高電平的時候 被 設備讀取。

After the stop bit is received, the device will acknowledge the received byte by bringing the Data line low and generating one last clock pulse.

在收到停止位之后,設備將通過拉低數據線,生成最后一個時鐘脈沖 來 應答收到的字節

If the host does not release the Data line after the 11th clock pulse, the device will continue to generate clock pulses until the the Data line is released (the device will then generate an error.)

在第11個時鐘脈沖之后,如果主機并沒有釋放數據線,設備將繼續產生時鐘脈沖,直到數據線被釋放(然后 設備將產生一個錯誤)

The host may abort transmission at time before the 11th clock pulse (acknowledge bit) by holding Clock low for at least 100 microseconds.

在第11個脈沖之前(回應位),主機可以隨時中止傳輸,只要拉低時鐘持續100us即可

|

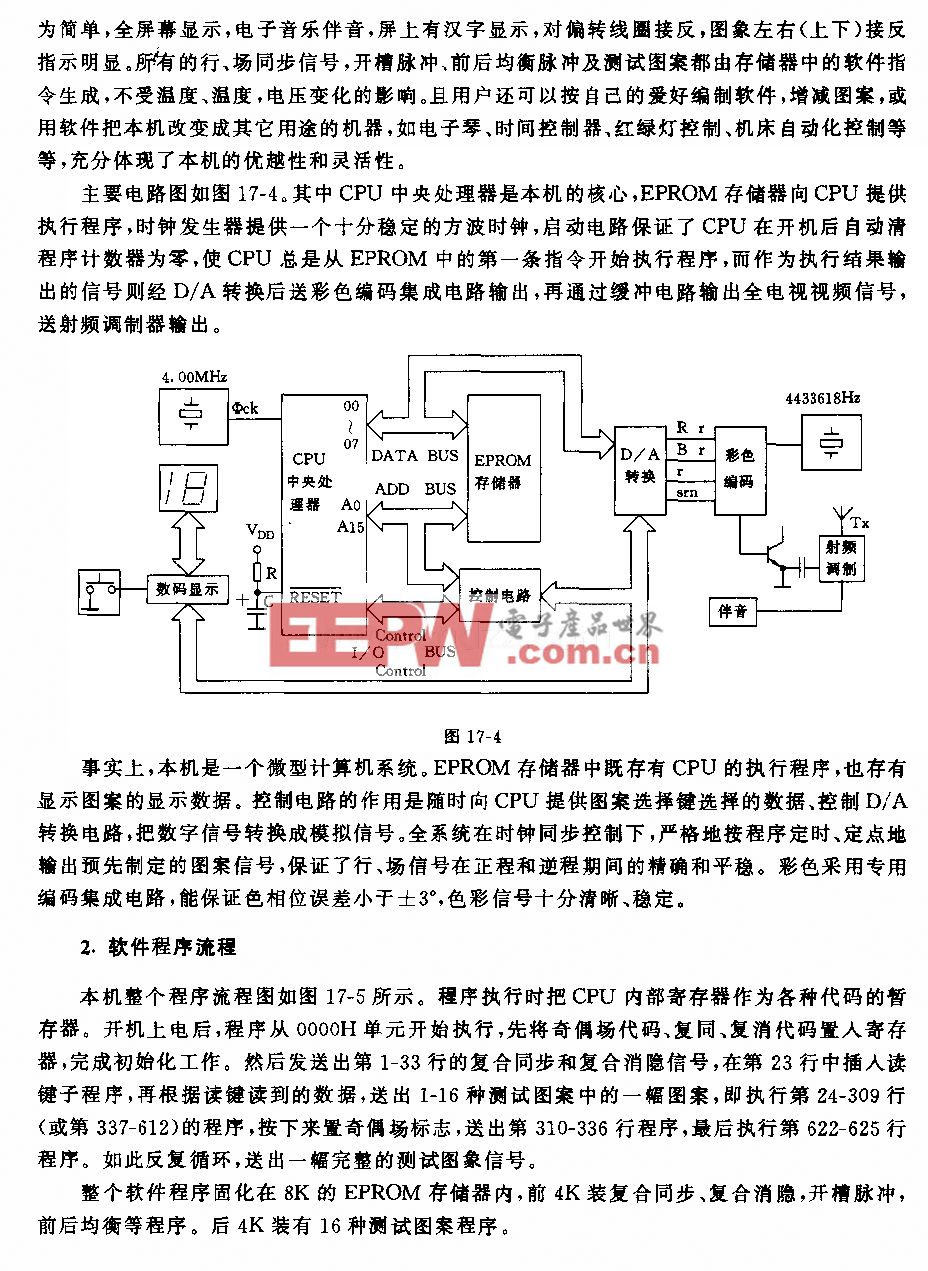

T9 == Time from inactive to active CLK transition, used to time when the auxiliary device samples DATA

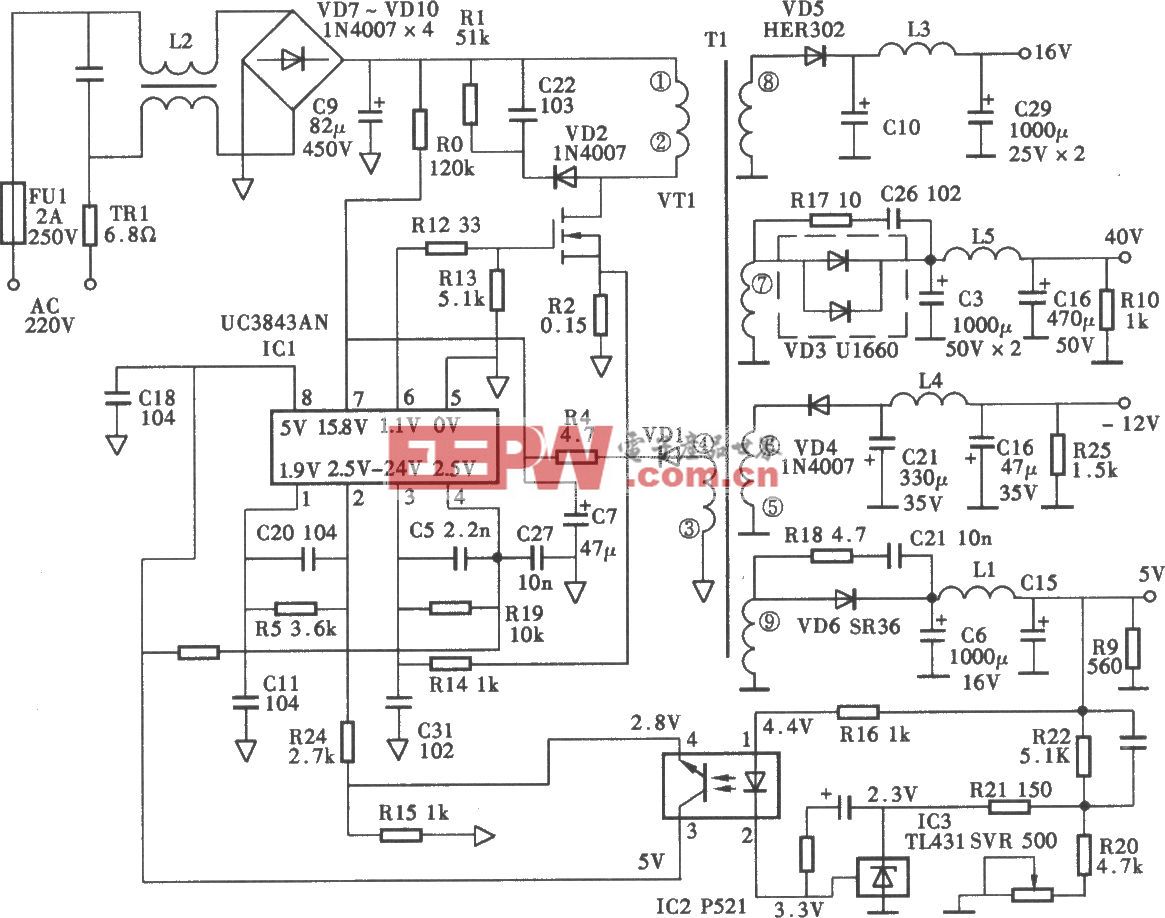

FreeScale(Moto)提供的時序圖

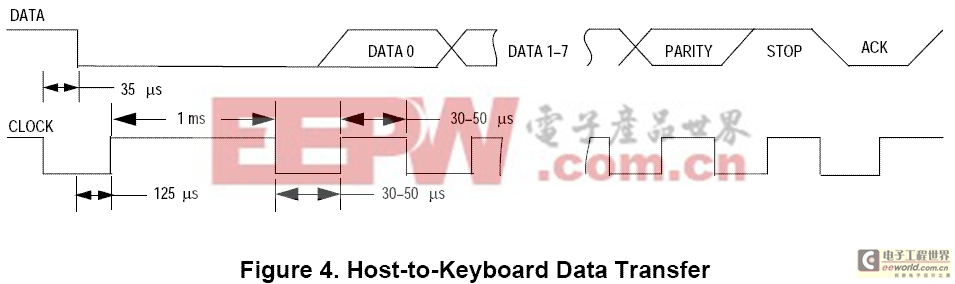

主機到鍵盤的數據傳輸

1.主機 通過拉低 時鐘線 來 啟動一個主機到鍵盤的數據傳輸。大約35us后,主機拉低數據線

。這個事件序列 就是 通知 鍵盤,主機要傳輸一個命令了。在數據信號的下降沿大約 125us 后 時鐘信號釋放,就被鍵盤內部的上拉電阻拉為高電平 。

2. 在時鐘信號的上升沿 約 1ms ,數據傳輸開始。這個期間,數據線保持低電平。鍵盤拉低時鐘線,clocking in the low data line. 這個就做傳輸的起始位。

3. 鍵盤用時鐘驅動 8個數據位從主機傳輸到自己這邊。 這個時鐘有50%的占空比(duty cycle).高電平和低電平的時間都在30~50us之間。主機在每個周期的低電平的時候改變數據線上的數據。在每個時鐘的上升沿5~25us之后鍵盤 開始從數據線上取樣,取出主機發來的數據。

4.數據位之后是一個奇偶校驗位(采用奇校驗)

5.最后是停止位

6.如果鍵盤讀到一個高電平的停止位,鍵盤就在 取樣停止位的那個時鐘的下降沿 之后的低電平期間 拉低數據線。這個行為叫做 鍵盤給主機的應答信號。

鍵盤拉高時鐘之后,也拉高數據線。

7.在收到一個字節后,鍵盤對接收的數據執行一個奇偶校驗。如果奇偶校驗錯誤,或者接收的數據無法識別為有效的命令,那么鍵盤請求重新發送(發送0xFE給主機)

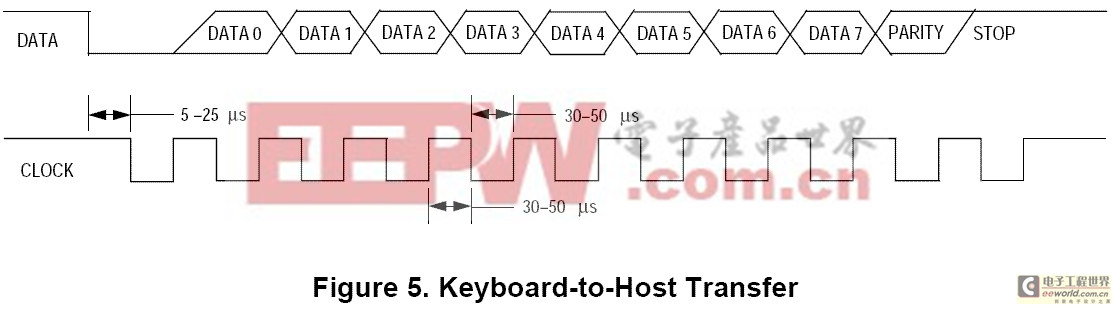

1. 鍵盤發送數據前,首先必須讓時鐘 和數據線都在鍵盤內部的上拉電阻作用下 拉成高電平。然后鍵盤拉低數據線,5-25us之后,鍵盤拉低時鐘線。在時鐘的下降沿,開始傳輸起始位The falling edge of the clock line clocks in the transfer’s start

bit.

2. 鍵盤用時鐘驅動 8個數據位到主機。 這個時鐘有50%的占空比(duty cycle).高電平和低電平的時間都在30~50us之間。鍵盤在每個周期的高電平的時候改變數據線上的數據。這個改變出現在時鐘的上升沿的5us后 和 下降沿的5us前。鍵盤的數據在時鐘的下降沿被鎖存進主機。

3.數據位之后是一個奇校驗位

4.最后是停止位。在時鐘的下降沿 0~50us之間 主機拉低時鐘 來鎖存停止位。這就告訴鍵盤主機現在忙,不能在接收 其他的鍵盤傳輸數據。在處理完接收的數據,準備好接收下一個數據之前,主機釋放時鐘。

6.在鍵盤傳輸數據到主機的過程中,主機任何時候都可以中斷這個傳輸,發送一個命令到鍵盤。主機拉低時鐘和數據線 即可中止傳輸。所以,鍵盤在時鐘為 低電平的時候必須取樣數據線。(無論什么時候輸出高數據位的時候)。在產生時鐘的上升沿時,必須讀取時鐘。

在任何時候發現這兩個條件不滿足,就拉高時鐘和數據線,放棄這次傳輸,并準備從 主機接收命令。

Moto 香港公司的 Derek Lau

當時鐘 高電平是,發送給主機的數據被主機讀取。在空閑狀態,時鐘和數據線都被拉為高電平。主機 拉低 時鐘最少100ms(?還是us)開始發送數據給鍵盤:

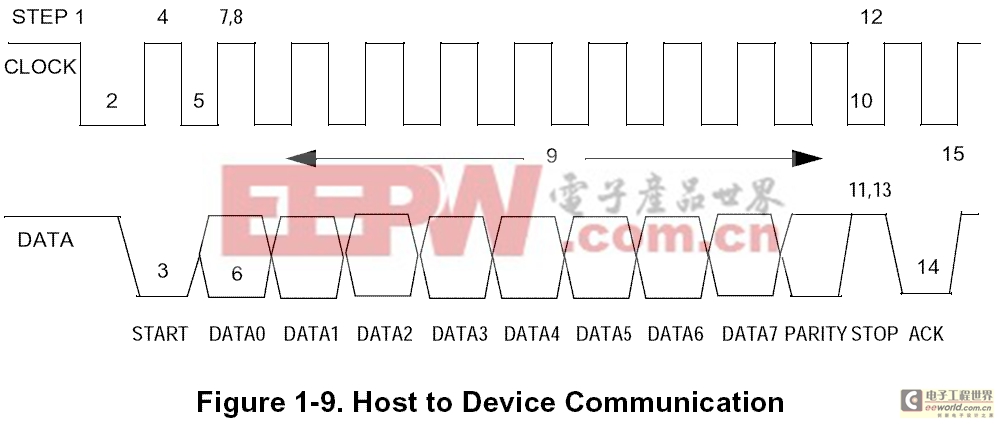

1.主機等待,直到沒有外部設備傳輸被處理

2.主機 拉低時鐘

3.主機拉低數據作為開始位

4 .主機釋放時鐘

5.設備拉低時鐘

6.主機發送數據

7.設備釋放時鐘,讀取數據

8.設備檢查時鐘線,如果時鐘為低,中止傳輸

9.重復 5-7步,發送 數據1-到數據0,以及 奇校驗位

10. 設備拉低時鐘

11. 主機釋放數據

12.設備時鐘時鐘

13.設備讀取數據線,想得到停止位,如果數據線為低(不是停止位),產生錯誤

14.設備拉低 時鐘和數據線

15.設備釋放 時鐘和數據線

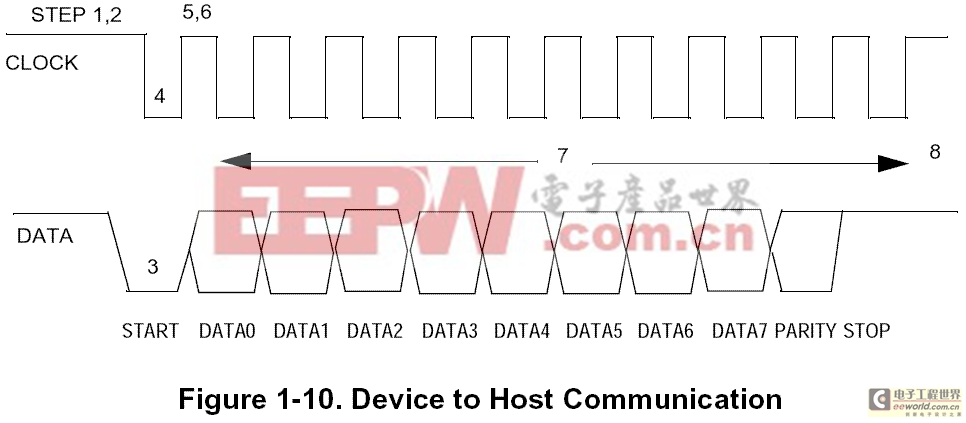

從設備發送到主機的數據,在時鐘的下降沿被讀取。在發送數據前,設備檢查通過檢測時鐘信號為高來得知 主機是否貯備好:

1.鍵盤(設備)等待時鐘為高(約50ms?us)

2.如果數據為 低,終止

3.鍵盤 發送數據

4.鍵盤拉低時鐘為低

5.鍵盤釋放時鐘為高

6.鍵盤 讀取時鐘線,如果時鐘為低,中止傳輸

7.重復 4-6步,傳輸數據0-數據7,

DIY機械鍵盤相關社區:機械鍵盤DIY

評論