基于壓控振蕩器(VCO)的高性能鎖相環(huán)(PLL)設

大多數(shù)商用分立VCO采用容值可變的變?nèi)荻O管,作為LC振蕩電路的可調(diào)諧元件。改變二極管的電壓會改變其電容,從而改變振蕩電路的諧振頻率。

變?nèi)荻O管的任何電壓噪聲都會被VCO增益KV(用MHz/V表示)放大,并轉(zhuǎn)換為相位噪聲。要使VCO相位噪聲保持最小,KV必須盡可能小,但為了實現(xiàn)合理的寬調(diào)諧范圍,KV必須較大。因此,對于要求低相位噪聲和寬調(diào)諧范圍的應用,VCO制造商通常會設計低增益、輸入電壓范圍較大的振蕩器,以滿足這些相互矛盾的要求。

窄帶VCO的典型電壓調(diào)諧范圍為0.5 V至4.5 V,寬帶VCO通常為1 V至14 V,某些情況下可以寬達1 V至28 V。

同軸諧振器振蕩器(CRO)是另一種特殊類型VCO,利用極低增益和寬輸入調(diào)諧電壓來實現(xiàn)超低相位噪聲,通常用于窄帶專用移動無線電和陸地移動無線電應用。

與高壓VCO接口

大多數(shù)商用PLL頻率合成器IC提供電荷泵輸出,其上限約為5.5 V;當環(huán)路濾波器僅使用無源器件時,VCO要求較高的調(diào)諧電壓,該輸出不足以直接驅(qū)動VCO。為了達到較高的調(diào)諧電壓,必須利用運算放大器電路實施有源環(huán)路濾波器拓撲結(jié)構(gòu)。

實現(xiàn)這種結(jié)構(gòu)的最簡單方法是在無源環(huán)路濾波器之后添加一個增益級。雖然易于設計,但這種方法有幾個缺點:反相運算放大器配置具有低輸入阻抗,會使無源環(huán)路濾波器承受負載,從而改變環(huán)路動態(tài)特性;同相配置具有足夠高的輸入阻抗,不會使濾波器承受負載,但有源濾波器增益會放大運算放大器的任何噪聲,從而無法受益于前置無源環(huán)路濾波器的濾波功能。更好的拓撲結(jié)構(gòu)是將增益級與濾波器集成于單一有源濾波器模塊中。建議采用前置濾波,避免來自電荷泵的極短電流脈沖過驅(qū)放大器,否則這可能會限制輸入電壓額定值。

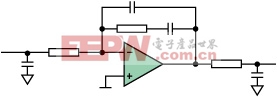

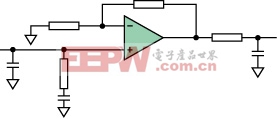

圖3顯示建議有源濾波器拓撲結(jié)構(gòu)的兩個示例,其中前置濾波分別使用反相和同相增益。請注意,這些放大器電路是真時間積分器,可強迫PLL環(huán)路在輸入端保持零誤差。環(huán)路之外,所示拓撲結(jié)構(gòu)可能會漂移至供電軌

a. 反相拓撲結(jié)構(gòu)

b. 同相拓撲結(jié)構(gòu)

圖3. 采用前置濾波的有源濾波器

反相拓撲結(jié)構(gòu)的優(yōu)勢是可以將電荷泵輸出偏置在固定電壓,通常為電荷泵電壓的一半(VP/2),此時對雜散性能最有利。注意應提供干凈的偏置電壓,最好是來源于ADP150等專用低噪聲線性穩(wěn)壓器,并在盡可能靠近運算放大器輸入引腳處充分去耦。分壓器網(wǎng)絡所用的電阻值應盡可能小,以便降低噪聲。使用反相拓撲結(jié)構(gòu)時,必須確保PLL IC允許PFD極性反轉(zhuǎn);如有必要,應抵消運算放大器的反轉(zhuǎn),以正確的極性驅(qū)動VCO。ADF4xxx系列就具有這種特性。

同相環(huán)路濾波器配置不需要專用偏置,因此這種解決方案可能更緊湊。此時,電荷泵電壓不是偏置在固定電平,而是在其工作電壓范圍內(nèi)變化。因此,采用此類濾波器時,使用具有軌到軌輸入的運算放大器更為關(guān)鍵。(下一節(jié)將說明輸入電壓范圍要求。)

選擇運算放大器

運算放大器的選擇對于最大限度地發(fā)揮有源濾波器的潛能至關(guān)重要。除帶寬外,需要考慮的主要性能規(guī)格有:

- 噪聲電壓密度,用nV/√Hz表示

- 電流噪聲,用pA/√Hz表示

- 輸入偏置電流

- 共模電壓范圍

濾波器輸出直接影響所產(chǎn)生的頻率和相位;因此,運算放大器的噪聲電壓密度可以顯示有源濾波器將增加多少相位噪聲。放大器噪聲在PLL環(huán)路帶寬內(nèi)和帶外均會產(chǎn)生影響,在環(huán)路濾波器的轉(zhuǎn)折頻率處最為顯著,具有高噪聲電壓密度的放大器尤其突出。因此,放大器噪聲必須保持較低水平,才能完成放大器和高壓VCO的使命,提供較低的相位噪聲。10 nV/√Hz以下是一個不錯的設計目標。與誤差電流脈沖相比,電流噪聲一般非常小,因此其影響往往比電壓噪聲小得多。

相對于PFD輸出電流,如果運算放大器具有較為明顯的輸入偏置電流,則可能會導致PLL輸出頻譜上出現(xiàn)較大的雜散。為使VCO調(diào)諧電壓保持恒定且PLL保持鎖定,電荷泵必須補償每個PFD周期中運算放大器輸入端所耗用的偏置電流。這就會在PFD頻率調(diào)制VTUNE電壓,并在載波周圍引起雜散,其偏移等于PFD頻率。輸入偏置電流越高,對VTUNE電壓的調(diào)制越大,雜散幅度越高。

共模電壓范圍或輸入電壓范圍(IVR)是運算放大器的另一個重要特性,但常被忽視,導致終端設計發(fā)生嚴重問題。IVR決定輸入引腳上最大/最小信號與正/負供電軌之間所需的間隙。

對于采用±15 V電源供電的早期運算放大器,典型IVR為±12 V。后來加入了緩慢的橫向PNP輸入級,使得IVR可以包括負供電軌,從而提供單電源工作能力。雖然任何運算放大器均能采用地和正電源供電,但必須注意輸入與供電軌的

分頻器相關(guān)文章:分頻器原理 電荷放大器相關(guān)文章:電荷放大器原理 鑒相器相關(guān)文章:鑒相器原理 數(shù)字濾波器相關(guān)文章:數(shù)字濾波器原理 鎖相環(huán)相關(guān)文章:鎖相環(huán)原理

評論