相位噪聲和抖動對系統性能的影響

在芯片級上,可以使用以下設計技術將抖動降至最低:

1.差分信號收發:即使進入芯片的是單端信號,最好也在芯片中將其轉換為差分信號,原因同上節所述。

2.仔細布設信號通路:在對敏感時序信號通路進行布線時必須小心,而且走線越短越好,還應避免與任何數字信號線交叉。只要條件允許,最好將這些信號通路均在屏幕上顯示出來。例如,一條在第二層金屬平面上的信號通路可以夾在第一層和第三層金屬平面之間,而第一層和第三層金屬平面均連接到一個干凈的地上。

3.恰當選擇緩沖器大小:如果用緩沖器在模塊間分配信號,那么必須注意驅動強度的選擇。驅動不足會造成信號上升/下降沿過緩,給噪聲以可乘之機。

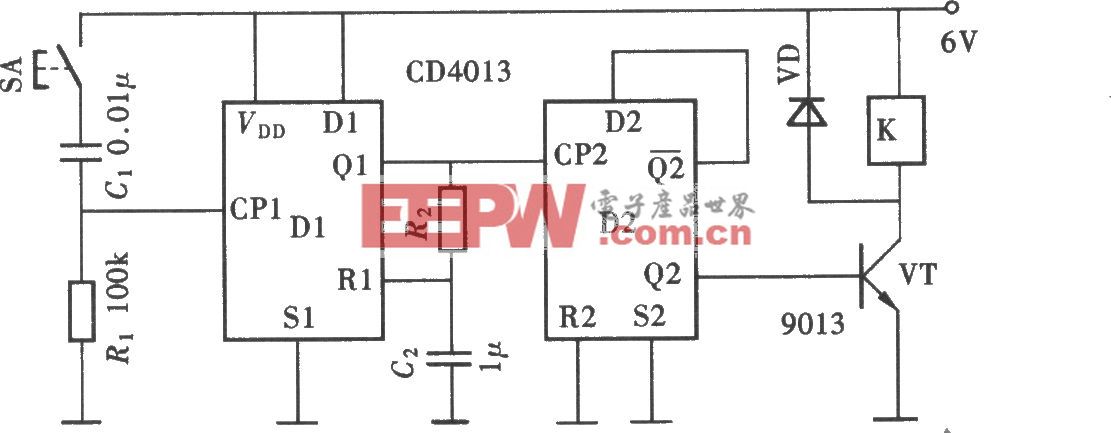

4.保持基底和地的干凈:基底噪聲和地噪聲是造成確定性抖動的主要原因。在一個有多路同步數字輸出的芯片內,地線反彈噪聲(ground bounce)可能會達到幾百毫伏,甚至1伏。為了降低地線反彈噪聲,芯片上應該有盡可能多的電源對,而且這些電源對應盡可能靠近數字輸出。

5.使用一個單獨的干凈地層:在電路設計中,最好將數字電路的電源與敏感的模擬電路(如振蕩器或PLL)的電源分開。數字電路,尤其是高驅動輸出數字電路的電源很可能會引入噪聲,而且這種電源一旦用于時序電路,那么也會成為增大抖動的一個主要原因。因此,對PLL這樣的電路甚至可以利用電源濾波來進一步減小電源噪聲的影響。

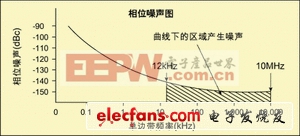

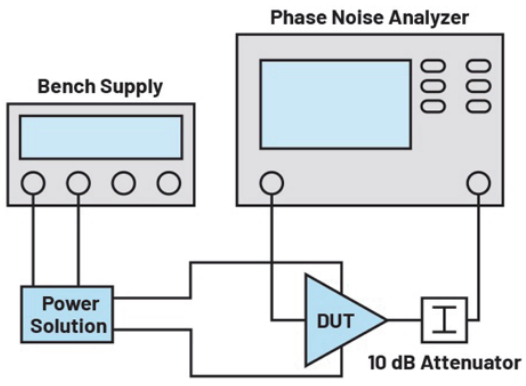

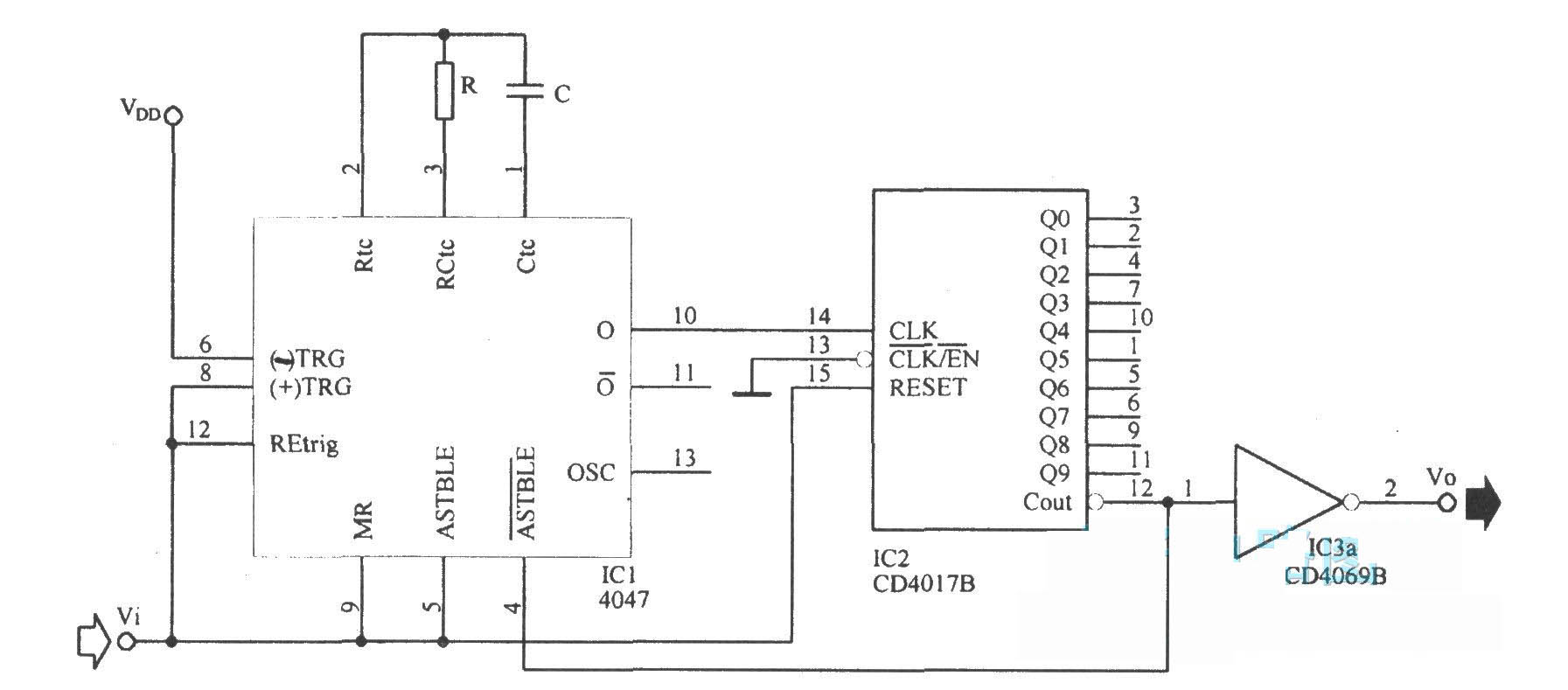

怎樣將單元模塊中的相位噪聲和抖動降至最低

在設計單元模塊時可以采用以下技術來減小抖動:1.利用尾電流--時序電路中使用的電流與相位噪聲之間有一個直接的關系。例如,增大一對差分對的尾電流必定導致抖動性能得到改善。于是我們就必須在降低抖動和縮減功耗之間尋求一個平衡,在適當之處選擇性地增大最敏感電路的電流。2.仔細布局--在對那些可能引起相位噪聲的單元進行布局時必須小心,匹配元件(例如連接到一對差分對的輸入)應方向相同,而且盡可能對稱布局。該方法會使應匹配的元件具有同樣的處理斜率(process gradients),因而有助于改善元件之間的匹配程度。電阻應盡可能寬,以減小Delta W效應。如果可能,應在整個電路中使用同一種類,甚至尺寸和阻值都相同的電阻來幫助跟蹤工藝和溫度的所有變化。

總而言之,要想盡可能減小抖動,就必須在所有設計層上都小心謹慎。高速數字設計師在設計過程的每一步都應考慮相位噪聲和抖動的影響。

評論