采樣時鐘抖動對ADC信噪比的影響及抖動時鐘電路

時鐘抖動的產生機制

直接測量時鐘抖動是比較困難的,一般采用間接測量的方法,為此本節首先給出時鐘抖動的產生機制。時鐘抖動是由時鐘產生電路(一般是基于低相位噪聲壓控振蕩器的鎖相環路)內部各種噪聲源所引起的,例如熱噪聲(主要是壓控振蕩器輸出信號的熱噪聲基底)、相位噪聲和雜散噪聲等,理論分析表明:當所需產生的頻率較高時,相位噪聲和雜散噪聲對時鐘抖動的惡化并不明顯。

一般來說,VCO輸出級放大器的熱噪聲基底可以看成有限帶寬的高斯白噪聲,其有效帶寬大約為工作頻率的兩倍。當VCO正確地調諧到需要的輸出頻率時,噪聲基底對抖動的影響可以用下面的公式計算:

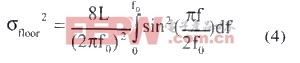

式中f0是振蕩器的中心頻率,f表示相對于中心頻率的偏移,L(f)是在頻率偏移f處的相位噪聲(單位是dBc/Hz)。為了進一步改進系統的性能,人們往往在VCO的輸出端使用一個頻率響應類似于帶通濾波器的功率匹配網絡,這對帶寬外的噪聲有一定的衰減作用。這樣,就能夠利用從0 Hz到f0區間內的積分估算最差情況下的噪聲,該范圍以外的噪聲被大大削弱,可以忽略,因為從0到f0范圍內的噪聲基底是平滑的,L(f)可視為常數,于是公式(3)簡化為:

故由噪聲基底引起的邊沿時鐘抖動為:

理論上可以認為從鎖相環路輸出信號的相位噪聲特性同VCO特性基本一致,但實際的鎖相電路會引入一定的噪聲,而VCO輸出放大器也會使產生的時鐘信號的相位噪聲特性變差。所以在進行鎖相環電路的設計時,除了選擇具有較低相位噪聲的VCO外,還應選擇具有較低噪聲系數的放大器或時鐘緩沖器,并盡量將時鐘產生電路與其它電路分隔開來。

基于低相位噪聲VCO的可變采樣時鐘

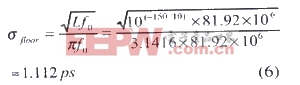

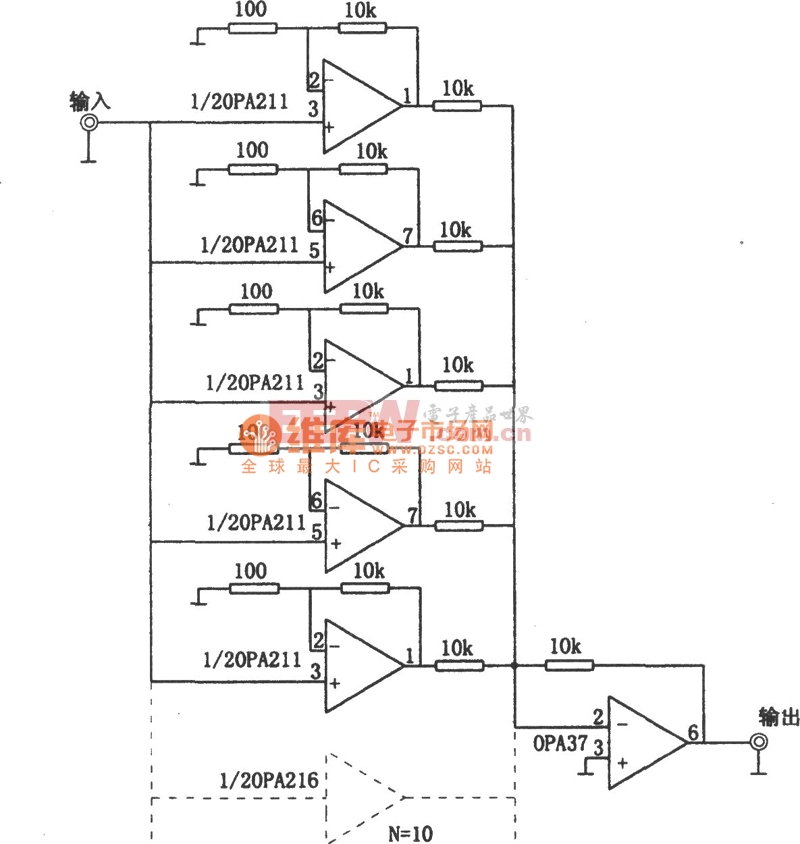

圖2給出了一個實用的基于低相位噪聲VCO的低抖動可變采樣時鐘產生電路。

圖2中以MC145170作為時鐘產生環路的頻率合成器,選用Mini-Circuits公司的低相位噪聲壓控振蕩器POS-200作為時鐘產生環路的VCO,由于POS-200的輸出信號要經過多次分路,所以在其輸出信號作第一次分路后,一路反饋送入MC145170作為輸入調諧信號,另一路則經低噪聲放大器放大后輸出,然后再作一次分路,一路作為ADC的采樣時鐘,另一路則送入DSP作為ADC采樣后數字信號的同步時鐘。由上面的分析可知,只要設計得當,上述的時鐘產生電路輸出信號的相位噪聲特性將主要取決于POS-200,POS-200在偏離中心頻率1MHz處的單邊相位噪聲為-150dBc/Hz,在估計鎖相環電路輸出信號的熱噪聲基底時可以采用該值,當鎖相環輸出信號頻率為81.92MHz時,由公式(5)可以計算出輸出時鐘信號的抖動為:

如果使用的ADC為AD9245,參照圖1可以看出:當ADC前端輸入信號頻率低于50MHz時,AD9245的信噪比將優于65dB,輸入信號頻率低于100MHz時,AD9245的信噪比將優于60dB。

評論