采樣時鐘抖動對ADC信噪比的影響及抖動時鐘電路

ADC是現(xiàn)代數(shù)字解調(diào)器和軟件無線電接收機中連接模擬信號處理部分和數(shù)字信號處理部分的橋梁,其性能在很大程度上決定了接收機的整體性能。在A/D轉(zhuǎn)換過程中引入的噪聲來源較多,主要包括熱噪聲、ADC電源的紋波、參考電平的紋波、采樣時鐘抖動引起的相位噪聲以及量化錯誤引起的噪聲等。除由量化錯誤引入的噪聲不可避免外,可以采取許多措施以減小到達ADC前的噪聲功率,如采用噪聲性能較好的放大器、合理的電路布局、合理設計采樣時鐘產(chǎn)生電路、合理設計ADC的供電以及采用退耦電容等。

本文主要討論采樣時鐘抖動對ADC信噪比性能的影響以及低抖動采樣時鐘電路的設計。

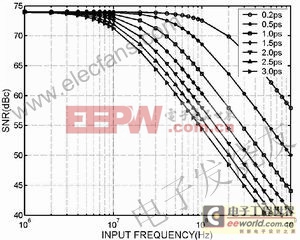

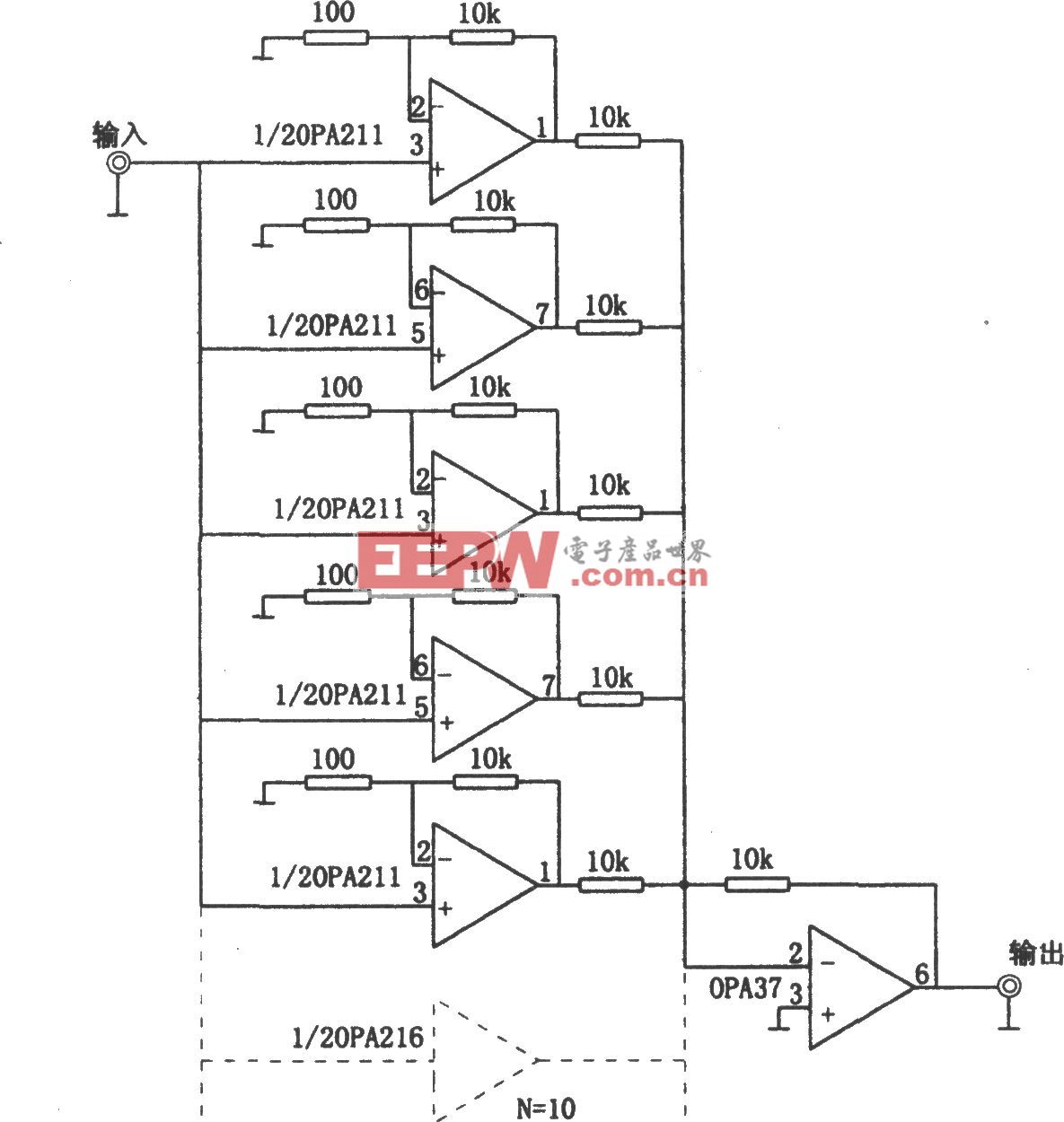

(a)12位ADC理想信噪比

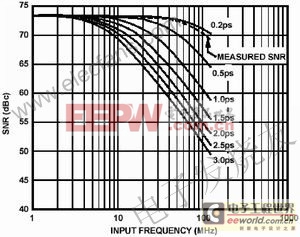

(b)AD9245實測信噪比

圖1 不同時鐘抖動情形下12位ADC的信噪比示意圖

時鐘抖動對ADC信噪比的影響

采樣時鐘的抖動是一個短期的、非積累性變量,表示數(shù)字信號的實際定時位置與其理想位置的時間偏差。時鐘源產(chǎn)生的抖動會使ADC的內(nèi)部電路錯誤地觸發(fā)采樣時間,結果造成模擬輸入信號在幅度上的誤采樣,從而惡化ADC的信噪比。歡迎轉(zhuǎn)載,本文來自電子發(fā)燒友網(wǎng)(http://www.elecfans.com)

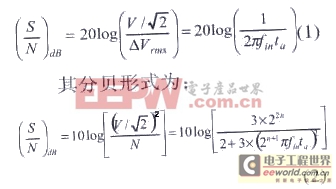

在時鐘抖動給定時,可以利用下面的公式計算出ADC的最大信噪比:

根據(jù)公式(2),圖1分別給出了量化位數(shù)為12-bit時不同時鐘抖動情形下ADC理想信噪比和實測信噪比示意圖。

由圖1可以看出時鐘的抖動對ADC信噪比性能的惡化影響是十分明顯的,相同時種抖動情形下進入到ADC的信號頻率越高,其性能惡化就越大,同一輸入信號頻率情形下,采樣時鐘抖動越大,則ADC信噪比性能惡化也越大。對比圖1中兩個示意圖可以看出實測的采樣時鐘抖動對ADC信噪比性能的影響同理論分析得到的結果是十分吻合的,這也證明了理論分析的正確性。因此,在實際應用時不能完全依據(jù)理想的信噪比公式來選擇A/D轉(zhuǎn)換芯片,而應該參考芯片制造商給出的實測性能曲線和所設計的采樣時鐘的抖動性能來合理選擇適合設計需要的A/D轉(zhuǎn)換芯片,并留出一定的設計裕量。

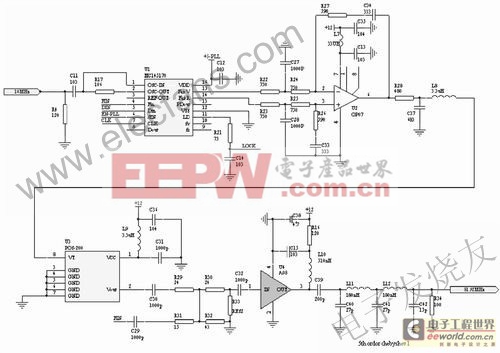

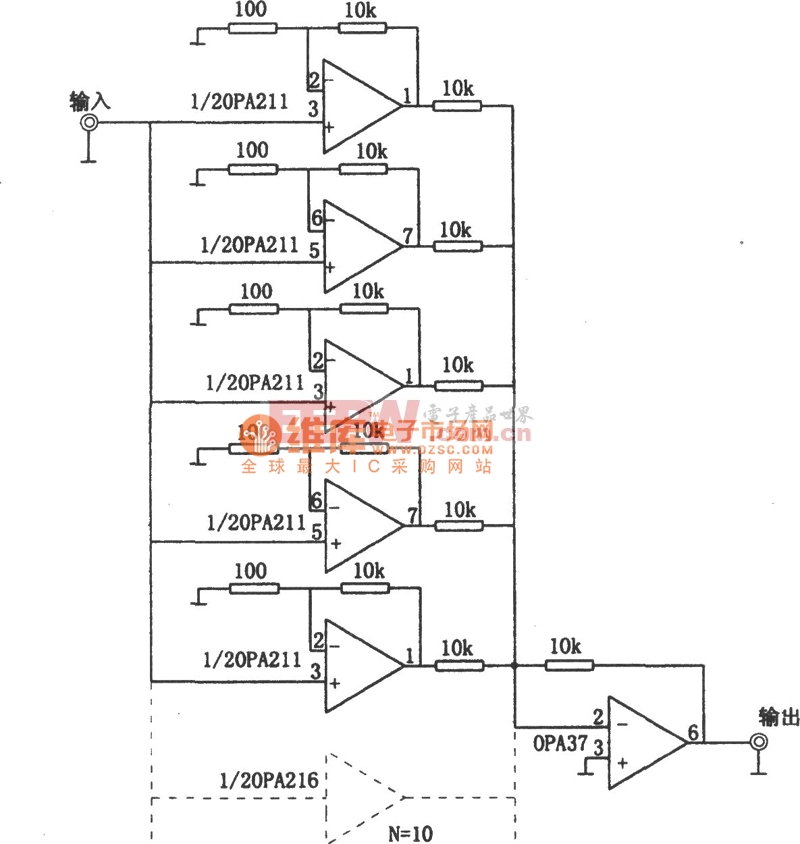

圖2 一個實用的低抖動時鐘產(chǎn)生電路

評論