基于Verilog實現電器定時開關控制

4.1按鍵掃描及鍵值讀取

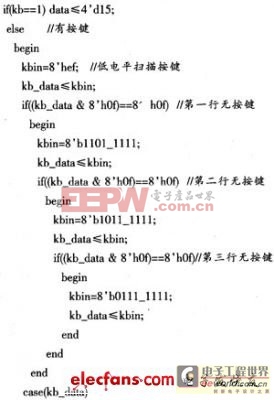

CPLD檢測到kb下降沿時,表示有鍵按下時,為防止按鍵抖動,延時一段時間再檢測,若確有鍵按下,CPLD采用低電平逐行掃描,待找到按鍵時,根據掃捕得到的數值,確定按鍵值。對于無效按鍵,設按鍵值為"15"。輸入信號kb的下降沿觸發對鍵值的讀取,可保證對于每一次按鍵,僅作一次處理。主要程序如下:

4.2功能鍵的判斷

程序初始化時為設定時間、開啟電器編號、電器開啟時間、電器關閉時間4個功能鍵設置對應按鍵值。定義功能標志寄存器fun,并使用格雷碼標志各個功能,相鄰兩個功能的編碼僅有一位不同,可避免狀態跳變,比目前常用的獨熱碼節省CPLD邏輯單元。由于本設計中寄存器fun只有5個狀態,選用3位格雷碼,并對編碼方式進行改進。根據上一步得到的按鍵值判斷具體要實現哪個功能,并依此設置fun的值,如下所示:

先根據鍵值判斷是哪一個數字鍵,再根據功能標志寄存器fun判斷進行哪項設置。若正在進行的是時間設置,則將時間寄存器左移4位,將數字值存入低位;若為設定需要開啟電器的編號狀態,則電器編號數組num對應位置"1",并通過電阻使相應發光二極管點亮,否則為"0";若為設定電器開啟時間狀態,相應電器的開啟時間寄存器timeon左移4位,將數字值存入低位;若為設定電器關閉時間狀態,相應電器的關閉時間寄存器timeoff左移4位,將數字值存人低位。若為無效按鍵,則不進行任何操作。

4.4數字鐘的工作

本系統設計作為數字鐘和定時器,對計時準確性要求較高.由有源晶體振蕩器提供系統時鐘,可保證其穩定度。在頂層模塊中對系統時鐘分頻,得到1 Hz時鐘,作為數字鐘部分行波時鐘。這樣減少了片內各觸發器之間的時鐘偏移,事實證明,對設計時序無不良影響。 先將沒定的時間送人小時、分鐘對應的寄存器hour和min,為了顯示和用戶操作方便,用6位二進制寄存器,以8421BCD碼表示時間。如果秒為8'h59則秒寄存器sec清零,分鐘值加1,若秒值末位為"9",則秒值末位清零,秒值十位加1。

4.5判斷電器的開啟和關閉

若當前時間與某個已定時的電器的開啟時間相同,則開啟寄存器數組on對應位輸出高電平,開啟對應電器;若與某個已定時的電器的關閉時間相同,則開啟寄存器數組on對應位輸出低電平,關閉對應電器。

評論