基于Verilog實現電器定時開關控制

1、前言

隨著當今社會工作和生活節奏的加快,人們對許多電器、儀器、設備的自動化要求也越來越高,但現有的許多電器還不具備定時開啟和關閉功能,許多需要在固定時間開關的裝置,還需人工值守和操作,因此設計帶有時鐘顯示功能的多個電器定時開關控制系統,具有實際意義。

2系統功能及操作

系統上電時復位,時鐘顯示為0時0分0秒,按下"時間"設置鍵設定時間,數字鐘開始工作,數碼管顯示當前時間;按下"開啟電器編號"設置鍵,再按下要定時開啟的電器編號,對應發光二極管亮,表示設置有效;按下"電器開啟時間"設置按鍵;再依次輸入4位十進制的小時和分鐘,作為開啟時間;按下"電器關閉時間"設置按鍵,再依次輸入4位十進制的小時和分鐘,作為關閉時間。至此定時開關設置完成,對于電飯鍋等具有保持功能的電器,則不用設置定時關閉。使用Verilog HDL編寫CPLD程序,理論上可同時設置多個電器的定時自動開啟,本設計可同時設置3個電器。

3硬件設計

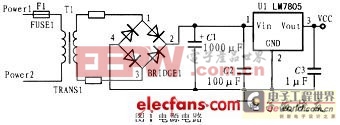

硬件設計采用Altera公司的CPLD EPM7128SLC84-6,簡化了外圍電路,穩定性和可靠性高,成本低。220 V、50 Hz工頻電源經變壓器、電橋整流后通過三端穩壓器,提供工作電壓,其電源電路如圖1所示。

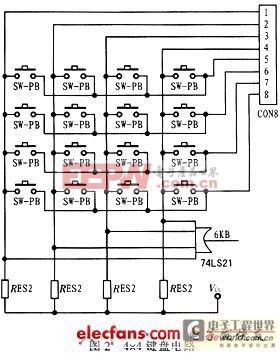

外接4×4鍵盤,使用較少的I/O端口線就可實現對較多按鍵的控制。當有鍵按下時,kb為低電平,CPLD的按鍵掃描部分采用動態掃描方式進行識別。設置14個按鍵,分別為0~9十個數字鍵和設定時間、開啟電器編號、電器開啟時間、電器關閉時間4個功能鍵,其余兩個留作功能擴展。4×4鍵盤電路如圖2所示。

本系統設計使用6個數碼管顯示時間,3個發光二極管標志是否定時。電器開啟信號經三極管放大后接繼電器,通過繼電器吸合導通電源線,開啟電器。

4軟件設計

Verilog HDL是硬件設計人員和QuartusⅡ界面之間的交互手段,其具體物理建模能力強,設計方便,可讀性好,語法類似C語言,與VHDL相比,更容易學習和掌握,與原理圖設計法相比,設計和分析更容易,可避免考慮畫面的布局及美觀

評論