EMCCD圖像傳感器CCD97時序驅動電路的設計

該系統(tǒng)選用的FPGA 芯片為Altera 公司Cyclone系列的FPGAEP1C3T 100, 其有100 個管腳封裝, I/ O的電源為3. 3 V , 內核電壓為1. 5 V, 有1 個鎖相環(huán)( PLL) , 2 個專用全局時鐘輸入管腳CLK0、CLK1, 5 個雙重用途時鐘管腳DPCLK。EP1C3T100 是SRAM 型的可編程邏輯器件, 本身并不能固化程序,因此需要通過一片F(xiàn)LASH 結構的配置芯片來存儲邏輯配置信息。

從Altera 公司提供的數(shù)據(jù)手冊, 可知Cy clo ne 系列的FPGA 僅支持EPCS1, EPCS4 以及EPCS16。而選用的EP1C3T 100 中, 其原始二進制文件大小為627 376 b, 使用EPCS1( 1 048 576 b) 的配置芯片。使用EPCS 配置芯片在主動串行模式( A S) 下( MSEL[ 0. . 1] 置地) , 即可實現(xiàn)上電后, 將存儲器件中的數(shù)據(jù)傳送到EP1C3T100 中。系統(tǒng)通過ARM 加載驅動程序實現(xiàn)對FPGA 的配置, 驅動FPGA 產生CCD 的工作時序。本系統(tǒng)選用Atmel 公司的AT 91RM9200 的處理器。它是基于ARM920T 內核, 主頻為180 MHz, 運行性能可達200 MIPS, 擁有獨立的16 KB 指令和數(shù)據(jù)Cache, 并配備有16 KB 的SRAM 以及128 KB的ROM。

EP1C3T 100 芯片內含1 個PLL, 外接40 MHz 有源晶振為PLL 提供時鐘。時鐘模塊通過Quartus 的megafunct ions 下的altpll 配置生成。采用非補償模式, 輸入/ 輸出時鐘比為5 :1, 輸出的2 路時鐘c0, c1 均為200 MHz。其中c0 為clk_gen 模塊提供基礎時鐘。

同時c1 產生相位需要調整的RΦ2HV, 用以滿足CCD97 增益寄存器轉移過程中的嚴格時序要求。

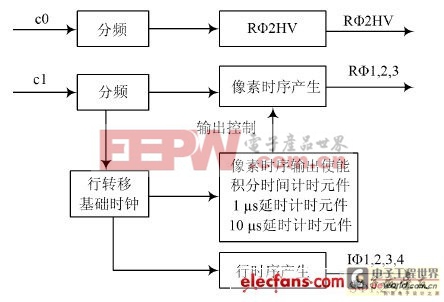

在FPGA 時序發(fā)生設計中, 依照CCD97 工作的流程, 進行逆序設計。從最高頻率的像素移位讀出時鐘到行轉移時鐘最后到幀轉移這樣的流程進行設計。框圖如圖4 所示。

圖4 驅動時序設計框圖

2. 2. 1 I Φ, S Φ, RΦ 驅動設計:

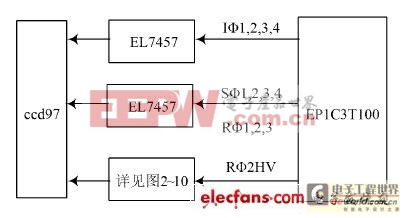

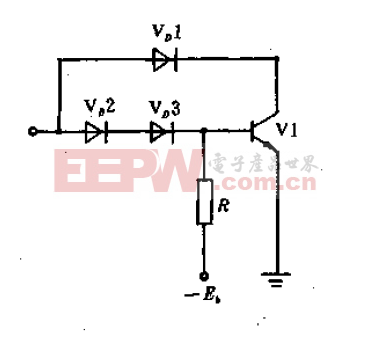

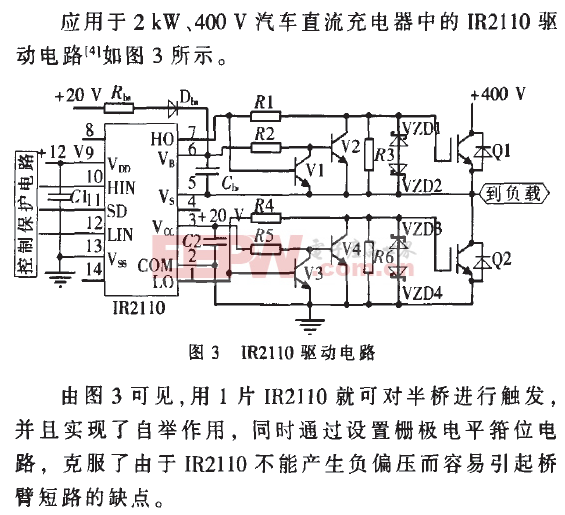

在設計I Φ, SΦ 以及RΦ驅動電路時, 統(tǒng)一采用Elantec 半導體公司的EL7457。它是高速四通道CMOS 驅動器, 能工作在40 MHz, 并提供2 A 的峰值驅動能力, 以及超低的等效阻抗( 3Ω ) , 它具有3 態(tài)輸出, 并通過OE 控制, 這對于CCD 的驅動來說, 容易實現(xiàn)靈活的電源管理。為了簡化設計, 固定RΦ2HV 的電壓幅值為典型值。在組成IΦ和S Φ 的驅動電路時必須考慮CCD97 驅動端的等效電容和電阻, 如表2 所示。

圖5 CCD97 驅動電路結構原理框圖

評論