適用于HDTV應用的8位DAC

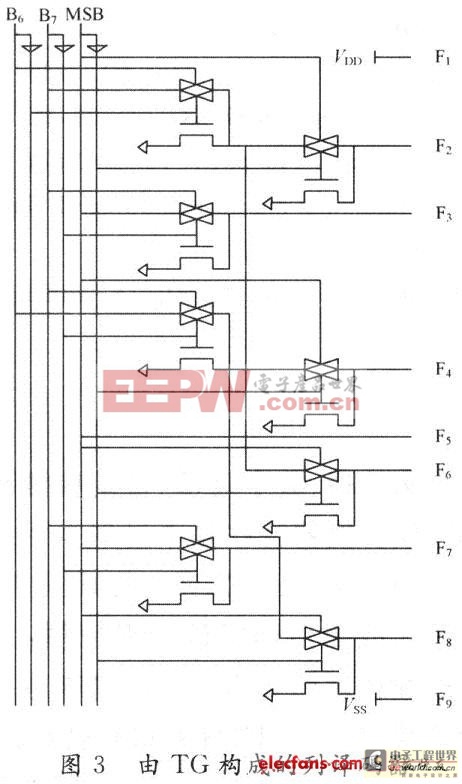

為減小功耗和減少延時,應該設計最少邏輯水平的行和列譯碼,運用TG邏輯電路組成3~8位行、列譯碼器。如此從高3位得到行譯碼器和從中間3位輸入得到列譯碼器。運用TG的行譯碼器電路如圖3所示。

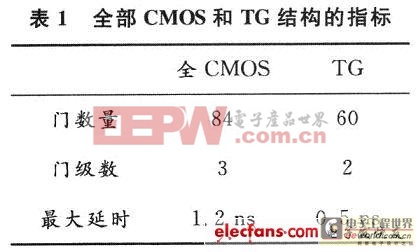

行譯碼器結構與列譯碼器基本相同,但沒有電源節點。使用TG邏輯譯碼器的另一巨大好處是可以減少晶體管的數量。在靜態邏輯,參考文獻[9]的譯碼器由84 只晶體管組成,但用TG結構組成的行和列譯碼器有30只晶體管,并且總數是60。這意味著芯片面積可能也被減少。較少的晶體管級數也幫助減少延時。另一方面,使用TG結構的邏輯門最大級數可減少到2級;不使用傳輸門結構的全CMOS結構的最高門級數是3,以上充分說明使用TG結構更有利減少延時和改進工作頻率。表1給出相關的參量對比。

2.3 工作原理

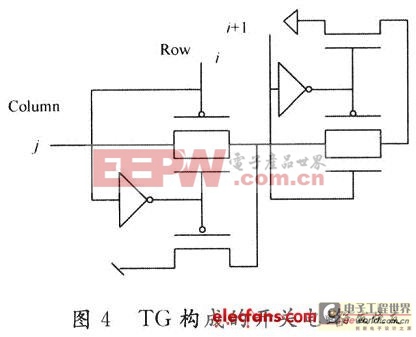

用行列譯碼器進行譯碼,單位電流源是導通還是截止,共有三種情況。第一種是所在行和下一行都是“1”,在這種情況下,無論列控制信號是否為“1”,該電流源均被選中。也就是說,對應的電流源開關狀態為接通狀態。第二種情況是所在的行控制信號為“1”,但是下一行的控制信號為“0”,這時,電流源是否被選中,要根據列控制信號來決定。如果列控制信號為“1”,則該電流源被選中;如果列控制信號為“0”,則該電流源不被選中,處于截止狀態。第三種情況是所在行和下一行的控制信號均為“0”,那么不管其所在列的控制信號為多少,此電流源不會被選中,處于截止狀態。TG構成的開關電路如圖4所示。

3 電流源電路及減少毛刺電路

電流源電路是DAC的重要部分,同時為了減小毛刺反應,下面將介紹減少毛刺的電路。

3.1 電流單元

一般常用的設計均采用減少電路噪聲和降低電流源的復雜結構。例如,差分電路、偏置電路、參考電流等需要很多數量的晶體管。在這個設計中,使用一個簡單的電流單元結構,并且電流源采用由二只晶體管組成的電流源單元。與其他芯片相比,電路的面積可以大大減小,如圖5所示。

評論