13bit 40MS/s流水線ADC中的采樣保持電路設(shè)計

本文對流水線ADC的采樣保持電路的結(jié)構(gòu)以及主要模塊如增益提高型運算放大器電路、共模反饋電路和開關(guān)電路進行了分析,并對各個模塊進行了設(shè)計,最終設(shè)計出一個適合于13 bit 40 MHz流水線ADC的采樣保持電路,仿真結(jié)果表明,該采樣保持電路滿足設(shè)計要求。

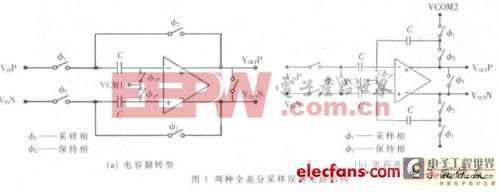

1 采樣保持電路結(jié)構(gòu)

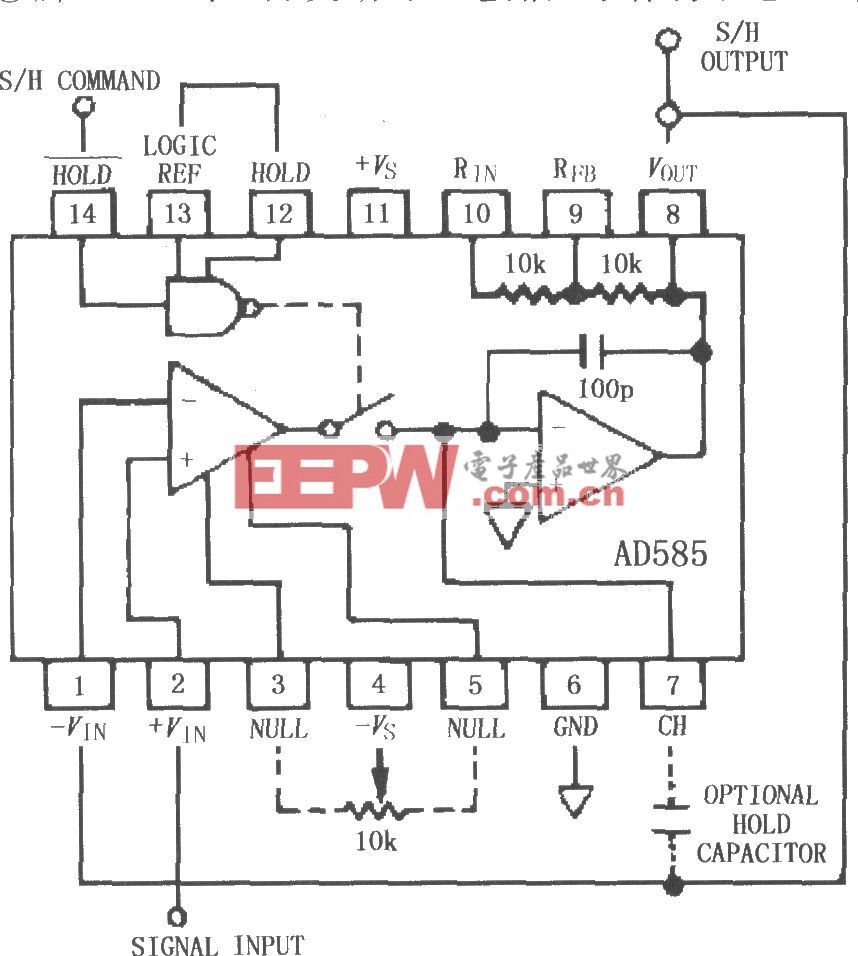

采樣保持電路的結(jié)構(gòu)直接決定了采樣保持電路的精度和速度,圖1為常用的兩種全差分結(jié)構(gòu):電荷再分布型和電容翻轉(zhuǎn)型。全差分結(jié)構(gòu)能夠很好地消除直流偏置和偶次諧波失真,并抑制來自襯底的共模噪聲。

與電荷再分布型結(jié)構(gòu)相比較,電容翻轉(zhuǎn)型結(jié)構(gòu)的反饋系數(shù)為1,是電荷轉(zhuǎn)移型(在Cs=Cf=C時,反饋系數(shù)為0.5)的兩倍,因此在同樣的閉環(huán)帶寬時,電容翻轉(zhuǎn)式結(jié)構(gòu)所要求的運放單位增益帶寬(GBW)只是電容電荷再分布式GBW的一半,所以電容翻轉(zhuǎn)型結(jié)構(gòu)具有功耗小的優(yōu)點[3]。另外由于電荷再分布型電路需要使用4個電容,但電容翻轉(zhuǎn)型只需要2個電容,在CMOS工藝中,電容需要大的實現(xiàn)面積,電容翻轉(zhuǎn)型結(jié)構(gòu)具有小的實現(xiàn)面積。因此,電容翻轉(zhuǎn)型更適合高速高精度的流水線ADC應(yīng)用,本文的采樣保持電路采用電容翻轉(zhuǎn)式結(jié)構(gòu)來實現(xiàn)。

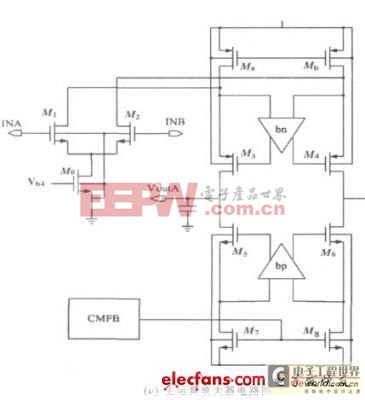

2 增益提高型放大器的設(shè)計

運算放大器是整個采樣保持電路中最重要的模塊,它的增益和帶寬直接決定了采樣保持電路的精度和速度。但增益和帶寬是相互矛盾的,高增益要求使用多級放大器、小的偏置電流、長溝道器件;而大帶寬則要求使用單級放大器、大的偏置電流、短溝道器件,所以放大器是采樣保持電路設(shè)計的一個難點。

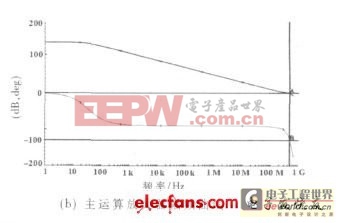

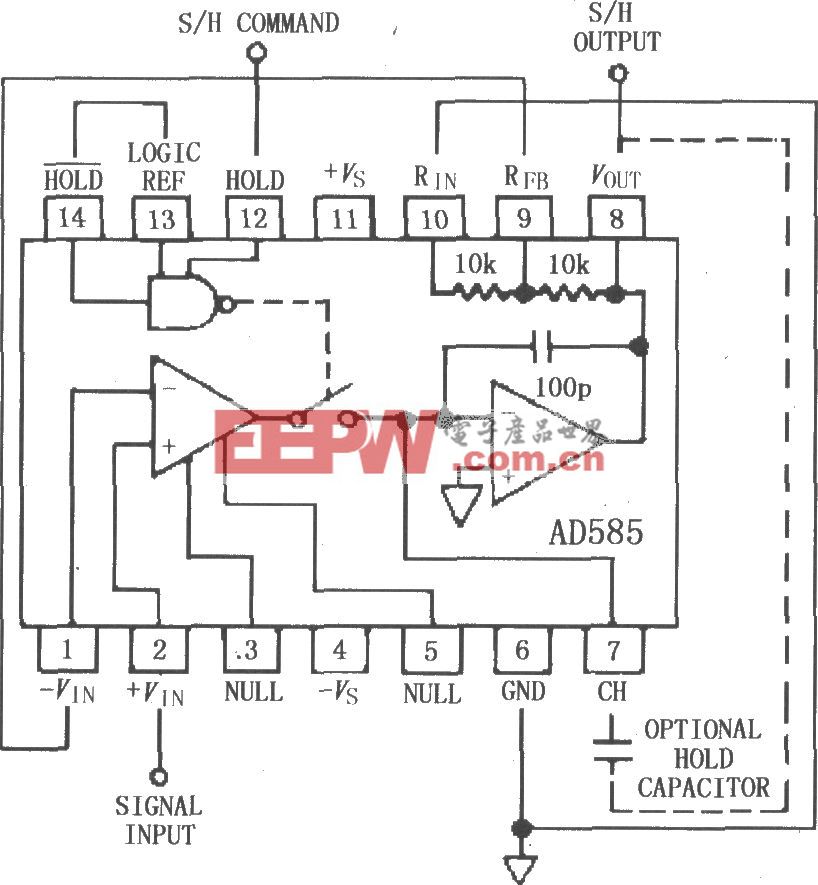

本文主運算放大器采用全差分的折疊式共源共柵結(jié)構(gòu),并用增益提高技術(shù)來提高放大器的增益,達到了高增益和大帶寬的要求[4-5]。主運算放大器電路如圖2 所示,由于NMOS管的遷移率高于PMOS管,在跨導(dǎo)相同的情況下,NMOS管具有較小的面積,從而使得運算放大器具有較小的輸入電容,有利于提高采樣保持電路的反饋系數(shù),所以本文采用了NMOS管作為輸入對管的折疊式共源共柵結(jié)構(gòu)。兩個輔助運算放大器BN和BP分別為NMOS和PMOS管作為輸入對管的折疊式共源共柵放大器。圖2 中的CMFB模塊為主運算放大器的共模反饋電路,由于主運放的輸出擺幅較大,所以采用如圖3(a)所示的開關(guān)電容共模反饋電路,開關(guān)電容共模反饋不會受輸出擺幅產(chǎn)生限制,并且其只有靜態(tài)功耗。對于兩個輔助運放而言,由于其輸出和輸入范圍很小,所以采用如圖3(b)所示的連續(xù)時間共模反饋電路,這種電路沒有電容,節(jié)省了面積。圖2(b)為主運算放大器在負載電容為6 pF時的頻率特性曲線,其增益為133 dB,帶寬約為478 MHz,相位余度為59.7度。整個放大器(包括偏置電路、輔助運放、共模反饋電路)消耗的平均電流為8.5 mA。

評論