適用于HDTV應用的8位DAC

在一般的數/模轉換器的設計中,譯碼結構通常采用分段結構。在一般的設計中,為了減少延時,通常使用鎖存器,同時配合復雜電流源結構,這種結構通常需要較大的能耗,并且采樣率不是足夠高。為了得到更高的采樣率和更好的線性度,在此基于TG結構,設計了單位電流單元矩陣和譯碼器電路,同時采用簡單的電流單元電路設計。

1 結構選擇

在此,采用電流舵型DAC設計。這是因為電壓型DAC所需元器件多,開關層數也較多,一般用于低速轉換器內;電荷型DAC隨精度的升高,面積急劇增大,而且對寄生電容敏感;電流型DAC具有高速的優勢,但不適用于低壓電路。電流舵型DAC是對電流型DAC的改進,常用于分段電路中。

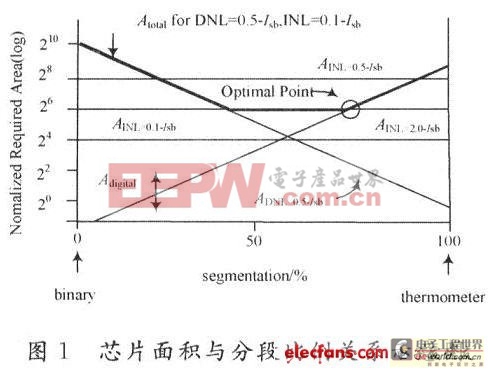

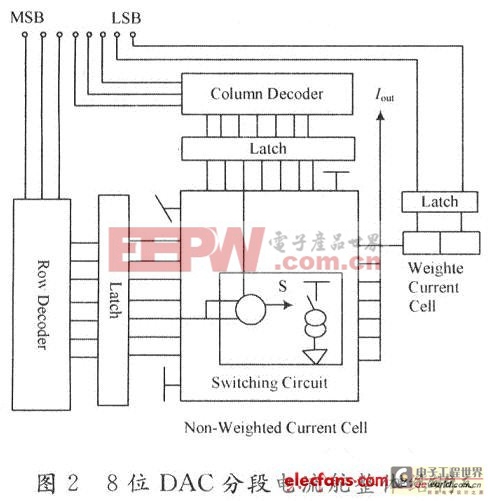

數/模轉換器的譯碼方式一般分為二進制、溫度計和分段式。溫度計譯碼方式相對二進制譯碼方式,在減小DNL和INL方面有很大的優勢,但是它的缺點是電路結構復雜。將二進制碼和溫度碼結合起來,就產生了分段結構。在對匹配要求、高精度的高位采用溫度計譯碼方式;低位采用二進制碼方式,可以減少面積。這種分段結構既有二進制碼結構簡單的長處,又有溫度碼良好的線性特性。在這個設計中,提出使用電流源矩陣邏輯電路構成的高速8位DAC,根據Lin和Bult做了面積與分段比的關系圖(見圖1),為了在速度、分辨率、功耗、芯片面積、電路性能等多個方面得到一個折衷結果,分段的高6位采用溫度計譯碼結構和低2位采用二進制譯碼結構。整個CS-DAC的結構如圖2所示。

圖2是一個說明8位分段式電流舵基本結構的例子。圖中采用6+2分段結構,高6位數字信號通過行譯碼器(Rows Decoders)、列譯碼器(Columns Decod-ers)轉換為溫度計碼,分別控制26-1=63個單位電流源,構成8×8電流源矩陣。多余的一個電流源作為Dummy器件,63個單位電流源和低2位二進制加權電流源的電流之和形成了陣列中整體電流源的電流。

2 譯碼邏輯電路

在DAC設計中,電流源單元、譯碼器和消除毛刺(噪聲)結構是重要部分,DAC的性能由這些部分決定。為了改進在高頻率動態線性,在此提出由傳輸門和晶體管組成組合邏輯譯碼電路。

2.1 傳輸門邏輯

因為NMOS管可以通過邏輯變量0傳輸,PMOS管可以通過邏輯變量1傳輸,用這兩個MOS平行放置構成互補結構。在此,可以得到傳輸門(TG),并且對于TG,邏輯變量0,1都可以很好的傳輸。大家都知道,譯碼器之間的延遲時間是毛刺發生的主要原因,并且與全部使用CMOS邏輯電路比較,用TG設計的邏輯電路性能更好,延遲更小。經過驗證,所有二輸入邏輯門的可由傳輸門和反相器組成。作為一個事例,實現與非門邏輯,全部CMOS技術要求6只晶體管,但采用TG結構只需要5只晶體管。在內在DAC芯片上,它有兩個信號,并且有翻轉信號,因此沒有反相器的需要,因而二只晶體管被減少。實驗結果說明,芯片面積和功耗的大大減少了。

2.2 邏輯譯碼電路

評論