ARM的未來低功耗系統設計發展之路

每一名系統設計人員都理解功耗和性能的相對關系:您的應用需要的計算性能越高,設計的功耗也就越高。但是,新一類應用對這一規則發出了挑戰。智能電話設計人員希望同時實現PC級峰值應用速率以及更長的電池使用壽命。嵌入式系統規劃采用智能傳感器以滿足嚴格的數據分析要求,安全的連接互聯網,但是要求最大限度的降低功耗。在傳統的思路中,這些明顯是無法實現的。但是,ARM工程師在6月份設計自動化大會(DAC)上的發言表明,CPU知識產權(IP)帶頭企業的發展方向卻是將這些不可能變為可能。

當然,ARM從開始出現便一直專用于低功耗計算。在其DAC主題發言中,ARM創始人之一Mike Muller從小劍橋計算機業余愛好供應商Acorn Computer公司一個芯片設計人員小組在1980年早期提出的問題開始,追溯了體系結構的發展:他們能使用RISC原理來開發16位微處理器,其性能超越個人計算機中的傳統芯片嗎?這一問題的答案是Acorn RISC機——ARM今后發展壯大的萌芽。

Acorn公司最初的成功源自高效的使用邏輯門和寄存器,主要是在簡潔的RISC體系結構的支撐下實現的。盡量減少每一操作所需的邏輯轉換數也一直是ARM套件的關鍵工具。但是,隨著公司在研發預算上的增長,以及公司影響的擴大,ARM設計人員開始在降低每一操作所需的功耗上尋求更好的工藝和電路技術。異步設計、低功耗工藝技術、精細粒度時鐘選通、電源選通以及動態電壓頻率調整(DVFS)等都成為工具套件的一部分。

Muller說,今天,ARM增加了新工具:超精細粒度電源選通,例如,以非常低的電壓進行工作等。但是,完全不同的發展方向將產生完全不同的技術:異構多核計算和虛擬化的概念——這是來自服務器領域的理念。

擴展低端

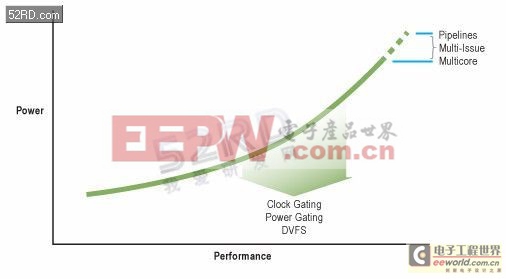

在評估功耗和性能的一張圖(圖1)上,不同的技術擴展了這張圖中不同位置的曲線。進一步使曲線向高性能方向擴展的技術包括,深度流水線、高時鐘頻率以及多核簇等。這些方法完全不同于功耗管理技術,功耗管理技術將整條曲線向低功耗方向下拉。兩者都具有的不同之處是新出現的一類技術,使曲線向下向左:超低功耗,低速計算。

Muller說,這是長壽命電池和低功耗的范圍。這里的問題是,怎樣以很低的能量來完成少量的計算。今天,異步CPU毫無爭議的占據了這一領域的制高點。只有當信號出現變化時才消耗動態功耗——而不是在每一次時鐘轉換時,因此,如果異步電路能夠克服其開銷邏輯的能耗成本,它將大幅度降低動態功耗。

但是,在高級工藝節點,特別是在較低時鐘頻率時,靜態功耗會大于動態功耗。因此,Muller關注的重點不是動態功耗,而是泄漏問題。

在高級工藝節點唯一降低泄漏真正有效的手段是降低工作電壓。Muller指出,問題是,當我們減小了器件尺寸后,很難調整晶體管閾值電壓Vt。我們目前所處的情景是,無法再進一步調整Vt以減小供電電壓,晶體管不能工作在傳統的飽和模式下。取決于所采用的傳統CMOS電路,一旦退出飽和模式后,會產生很強的源極漏極電流,還會進行快速開關。

Muller解釋說,但這并不意味著一點辦法都沒有。我們還是能夠減小工作電壓VDD,使電流足夠快,直至系統滿足性能要求。只要不太靠近Vt,我們可以采用的技術是DVFS。而Muller則闡述了更激進的一些想法。

第一個是關斷所有電源,把泄漏降到零。很顯然,粗粒度電源選通是有效的方法——例如,沒有使用的模塊。Muller指出,消耗很大的電能來迅速執行一項任務,然后關斷電源,這樣做通常可以節省能量。但還有更有趣的想法。

非常慢的運行

評論