基于PCB模擬設(shè)計的良好接地指導原則

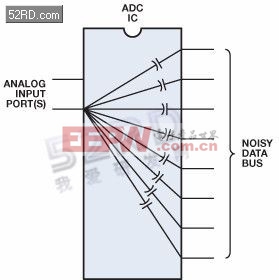

ADC輸出與緩沖寄存器輸入間的串聯(lián)電阻(圖4中標示為“R”)有助于將數(shù)字瞬態(tài)電流降至最低,這些電流可能影響轉(zhuǎn)換器性能。電阻可將數(shù)字輸出驅(qū)動器與緩沖寄存器輸入的電容隔離開。此外,由串聯(lián)電阻和緩沖寄存器輸入電容構(gòu)成的RC網(wǎng)絡(luò)用作低通濾波器,以減緩快速邊沿。

典型CMOS柵極與PCB走線和通孔結(jié)合在一起,將產(chǎn)生約10 pF的負載。如果無隔離電阻,1 V/ns的邏輯輸出壓擺率將產(chǎn)生10 mA的動態(tài)電流:

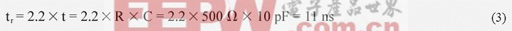

驅(qū)動10 pF的寄存器輸入電容時,500 Ω串聯(lián)電阻可將瞬態(tài)輸出電流降至最低,并產(chǎn)生約11 ns的上升和下降時間:

由于TTL寄存器具有較高輸入電容,可明顯增加動態(tài)開關(guān)電流,因此應(yīng)避免使用

緩沖寄存器和其他數(shù)字電路應(yīng)接地并去耦至PC板的數(shù)字接地層。請注意,模擬與數(shù)字接地層間的任何噪聲均可降低轉(zhuǎn)換器數(shù)字接口上的噪聲裕量。由于數(shù)字噪聲抗擾度在數(shù)百或數(shù)千毫伏水平,因此一般不太可能有問題。模擬接地層噪聲通常不高,但如果數(shù)字接地層上的噪聲(相對于模擬接地層)超過數(shù)百毫伏,則應(yīng)采取措施減小數(shù)字接地層阻抗,以將數(shù)字噪聲裕量保持在可接受的水平。任何情況下,兩個接地層之間的電壓不得超過300 mV,否則IC可能受損。

最好提供針對模擬電路和數(shù)字電路的獨立電源。模擬電源應(yīng)當用于為轉(zhuǎn)換器供電。如果轉(zhuǎn)換器具有指定的數(shù)字電源引腳(VD),應(yīng)采用獨立模擬電源供電,或者如圖6所示進行濾波。所有轉(zhuǎn)換器電源引腳應(yīng)去耦至模擬接地層,所有邏輯電路電源引腳應(yīng)去耦至數(shù)字接地層,如圖6所示。如果數(shù)字電源相對安靜,則可以使用它為模擬電路供電,但要特別小心。

某些情況下,不可能將VD連接到模擬電源。一些高速IC可能采用+5 V電源為其模擬電路供電,而采用+3.3 V或更小電源為數(shù)字接口供電,以便與外部邏輯接口。這種情況下,IC的+3.3 V引腳應(yīng)直接去耦至模擬接地層。另外建議將鐵氧體磁珠與電源走線串聯(lián),以便將引腳連接到+3.3 V數(shù)字邏輯電源。

采樣時鐘產(chǎn)生電路應(yīng)與模擬電路同樣對待,也接地并深度去耦至模擬接地層。采樣時鐘上的相位

評論