基于PCB模擬設計的良好接地指導原則

保持低阻抗大面積接地層對目前所有模擬電路都很重要。接地層不僅用作去耦高頻電流(源于快速數字邏輯)的低阻抗返回路徑,還能將EMI/RFI輻射降至最低。由于接地層的屏蔽作用,電路受外部EMI/RFI的影響也會降低。

接地層還允許使用傳輸線路技術(微帶線或帶狀線)傳輸高速數字或模擬信號,此類技術需要可控阻抗。

由于“總線(bus wire)”在大多數邏輯轉換等效頻率下具有阻抗,將其用作“地”完全不能接受。例如,#22標準導線具有約20 nH/in的電感。由邏輯信號產生的壓擺率為10 mA/ns的瞬態電流,流經1英寸該導線時將形成200 mV的無用壓降:

對于具有2 V峰峰值范圍的信號,此壓降會轉化為大約200 mV或10%的誤差(大約“3.5位精度”)。即使在全數字電路中,該誤差也會大幅降低邏輯噪聲裕量。

圖2顯示數字返回電流調制模擬返回電流的情況(頂圖)。接地返回導線電感和電阻由模擬和數字電路共享,這會造成相互影響,最終產生誤差。一個可能的解決方案是讓數字返回電流路徑直接流向GND REF,如底圖所示。這顯示了“星型”或單點接地系統的基本概念。在包含多個高頻返回路徑的系統中很難實現真正的單點接地。因為各返回電流導線的物理長度將引入寄生電阻和電感,所以獲得低阻抗高頻接地就很困難。實際操作中,電流回路必須由大面積接地層組成,以便獲取高頻電流下的低阻抗。如果無低阻抗接地層,則幾乎不可能避免上述共享阻抗,特別是在高頻下。

所有集成電路接地引腳應直接焊接到低阻抗接地層,從而將串聯電感和電阻降至最低。對于高速器件,不推薦使用傳統IC插槽。即使是“小尺寸”插槽,額外電感和電容也可能引入無用的共享路徑,從而破壞器件性能。如果插槽必須配合DIP封裝使用,例如在制作原型時,個別“引腳插槽”或“籠式插座”是可以接受的。以上引腳插槽提供封蓋和無封蓋兩種版本。由于使用彈簧加載金觸點,確保了IC引腳具有良好的電氣和機械連接。不過,反復插拔可能降低其性能。

應使用低電感、表面貼裝陶瓷電容,將電源引腳直接去耦至接地層。如果必須使用通孔式陶瓷電容,則它們的引腳長度應該小于1 mm。陶瓷電容應盡量靠近IC電源引腳。噪聲過濾還可能需要鐵氧體磁珠。

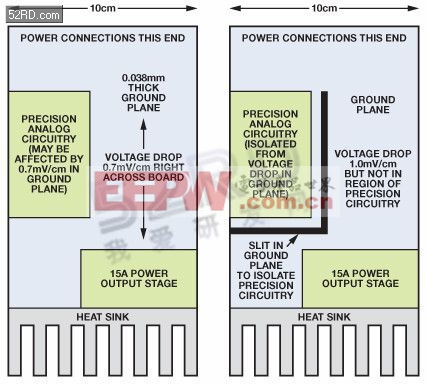

這樣的話,可以說“地”越多越好嗎?接地層能解決許多地阻抗問題,但并不能全部解決。即使是一片連續的銅箔,也會有殘留電阻和電感;在特定情況下,這些就足以妨礙電路正常工作。圖3說明了這個問題,并給出了解決方法。

評論