集成電路和信號完整性的設計

在您努力想要穩定板上的各種信號時,信號完整性問題會帶來一些麻煩。IBIS 模型是解決這些問題的一種簡單方法。您可以利用IBIS模型提取出一些重要的變量,用于進行信號完整性計算和尋找PCB設計的解決方案。您從IBIS模型提取的各種值是信號完整性設計計算不可或缺的組成部分。

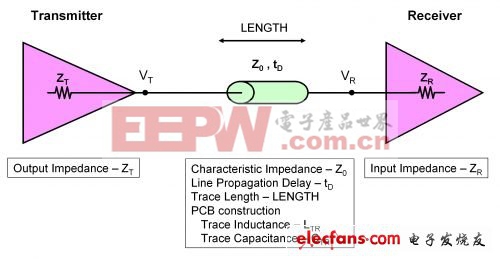

當您在您的系統中處理傳輸線路匹配問題時,您需要了解集成電路和PCB線路的電阻抗和特性。圖1顯示了一條單端傳輸線路的結構圖。

圖1連接發射器、傳輸線路和接收器組件的單端傳輸線路

就傳輸線路而言,我們可以從IC IBIS模型提取IC的發射器輸出阻抗 (ZT, Ω)和接收器輸入阻抗(ZR, Ω)。許多時候,IC 廠商產品說明書中并沒有說明這些集成電路 (IC) 規范,但是您可以通過IBIS模型獲得所有這些值。

您可以用下面四個參數定義傳輸線路:特性阻抗(Z0, Ω)、板傳播延遲(D, ps/in)、線路傳播延遲(tD,秒)和線跡長度(LENGTH,英寸)。一般而言,FR-4 電路板的Z0范圍為50Ω到75Ω,而D的范圍為140 ps/in到180 ps/in。Z0和D 的實際值取決于實際傳輸線路的材料和物理尺寸(《參考文獻1》)。特定電路板上的線路延遲(tD)等于傳播延遲(D)乘以您所使用線跡的長度(LENGTH)。所有板的計算方法均為:

D = 1012? (CTR* LTR) or

D = 85 ps/in *? (er)

Z0= ?(LTR/CTR)

tD= D * LENGTH

使用FR-4板時,合理的帶狀線傳播延遲為178 ps/英寸,特性阻抗為50Ω。

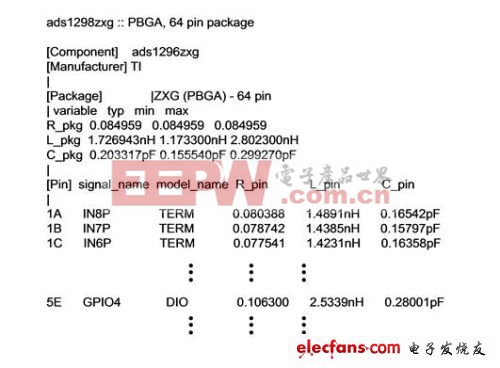

用于信號完整性評估的發射器規格為輸出阻抗 (ZT)。確定輸出阻抗時,IBIS 模型中的[Pin]區提供每個引腳的電阻、電感和電容寄生值。之后,您可以將封裝電容與各個緩沖器的電容值(C_comp)放在一起,以便于更清楚地了解。

正如[Pin]關鍵字上面的[Component]、[Manufacturer] 和[Package]描述的那樣,[Pin] 關鍵字與具體的封裝有關。您會在[Pin]關鍵字表中找到封裝電容和電感,因為它與引腳有關。例如,在ads129x.ibs模型中(《參考文獻2》),圖2表明了在哪里可以找到引腳5E(PBGA,64 引腳封裝)信號GPIO4的L_pin值和C_pin值。

圖2包括C_pin值在內的ads1296zxg封裝的封裝列表

該信號和封裝的L_pin(引腳電感)和C_pin(引腳電容)分別為1.489 Nh和 0.28001 pF。

評論