數字頻率合成精解:用DDS器件產生高質量波形

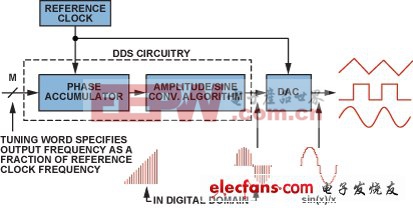

M為調諧字的分辨率(24至48位)

N為對應于相位累加器輸出字最小增量相位變化的fC的脈沖數。

圖2.典型的DDS架構和信號路徑(帶DAC)。

由于更改N會立即改變輸出相位和頻率,因此,系統自身具有相位連續,特點,這是許多應用的關鍵屬性之一。無需環路建立時間,這與模擬系統不同,如鎖相環 (PLL)。

DAC通常為一個高性能電路,專門針對DDS內核(相位累加器和相幅轉換器)而設計。多數情況下,結果形成的器件(通常為單芯片)一般稱為純DDS或C-DDS。

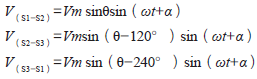

實際的DDS器件一般集成多個寄存器,以實現不同的頻率和相位調制方案。如相位寄存器,其存儲的相位內容被加在相位累加器的輸出相位上。這樣,可以對應于一個相位調諧字延遲輸出正弦波的相位。對于通信系統相位調制應用,這非常有用。加法器電路的分辨率決定著相位調諧字的位數,因此,也決定著延遲的分辨率。

在單個器件上集成一個DDS引擎和一個DAC既有優點也有缺點,但是,無論集成與否,都需要一個DAC來產生純度超高的高品質模擬信號。DAC將數字正弦輸出轉換為一個模擬正弦波,可能是單端,也可能是差分。一些關鍵要求是低相位噪聲、優秀的寬帶(WB)和窄帶(NB)無雜散動態范圍 (SFDR)以及低功耗。如果是外部器件,則DAC必須足夠快以處理信號,因此,內置并行端口的器件非常常見。

DDS與其他解決方案

其他產生頻率的方法包括模擬鎖相環(PLL),時鐘發生器和利用FPGA對DAC的輸出進行動態編程。通過考察頻譜性能和功耗,可以對這些技術進行簡單的比較,表1以定性方式展示了比較結果

表1.DDS與競爭技術——高級比較

鎖相環是一種反饋環路,其組成部分為:一個相位比較器, 一個除法器和一個壓控制振蕩器 (VCO)。 相位比較器將基準頻率與輸出頻率(通常是輸出頻率的N)分頻)進行比較。相位比較器產生的誤差電壓用于調節VCO,從而輸出頻率。當環路建立后,輸出將在頻率和/或相位上與參考頻率保持一種精確的關系。PLL長期以來一直被認為是在特定頻帶范圍內要求高保真度和穩定信號的低相位噪聲和高無雜散動態范圍 (SFDR) 應用的理想選擇。

由于PLL無法精確、快速地調諧頻率輸出和波形,而且響應較慢,這限制了它們對于快速跳頻和部分頻移鍵控和相移鍵控應用的適用性。

其他方案,包括集成DDS引擎的現場可編程門陣列 (FPGAs) ——配合現成DAC以合成輸出正弦波——雖然可以解決PLL的跳頻問題,但也存在自身的缺陷。主要系統缺陷包括較高的工作和接口功耗要求、成本較高、尺寸較大,而且系統開發人員還須考慮額外的軟件、硬件和存儲器問題。例如,利用現代FPGA中的DDS引擎選項,要產生動態范圍為60 dB的10 MHz輸出信號,需要多達72 kB的存儲器空間。另外,設計師需要接受并熟悉細微權衡和DDS內核的架構。。

評論