Δ-∑ADC(第四部分):噪聲與數(shù)據(jù)速率研究

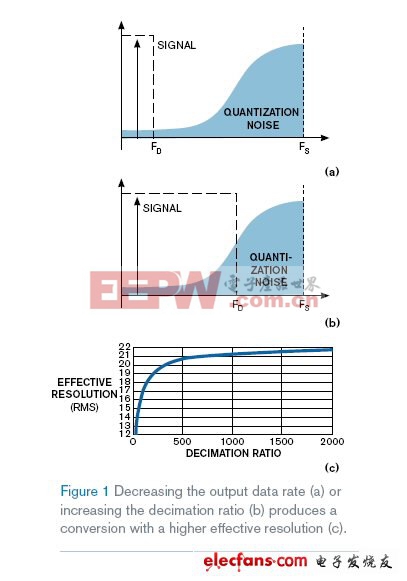

請(qǐng)看下面圖 1 中的頻譜。假設(shè)輸出數(shù)據(jù)速率為調(diào)制器采樣頻率的一小部分(請(qǐng)參見(jiàn)圖 1a),0~FD 的輸入頻率均在輸出信號(hào)頻帶中。由于噪聲水平較低,因此有效精度較高。FD 的更高頻率不但增加了轉(zhuǎn)換器的輸出數(shù)據(jù)速率,而且還降低了有效精度。雖然調(diào)制器的大部分噪聲都出現(xiàn)在更高頻率中,但是您獲得的有效精度仍然較低(請(qǐng)參見(jiàn)圖 1b)。圖 1c 就顯示了一個(gè)關(guān)于抽取比與采樣 ADC 有效精度之間關(guān)系的例子。

在不改變有效精度的條件下,提高輸出數(shù)據(jù)速率的一種方法就是提高調(diào)制器的采樣速率。您可以通過(guò)提高 Δ-Σ ADC 的主時(shí)鐘速率來(lái)提高這一速率。使用恒定抽取比后,采樣速率和功耗同時(shí)升高。此外,大多數(shù)轉(zhuǎn)換器都擁有采樣速率的實(shí)際極限,超過(guò)這一極限后其將無(wú)法正常地工作。抽取比和有效精度之間存在著緊密的聯(lián)系。保持采樣速率恒定不變并保持較低的數(shù)據(jù)速率,能夠讓您獲得較高的轉(zhuǎn)換器輸出有效精度。

評(píng)論