新型低功耗兩級運算放大器設計方案

隨著IC設計集成度和復雜度日益增加,如何進行低功耗設計已成為了一個必須解決的問題。目前實現低壓模擬電路的方法主要有三種:亞閾值,襯底驅動和浮柵設計。采用亞閾值特性實現的低功耗電路主要是利用了MOS 晶體管在進入亞閾值區域時漏極電流不是馬上消失,而是與柵控電壓呈一個指數關系,每當電壓下降80mV時,電流下降一個數量級,從而使功耗變小。但由于亞閾值電路的電流驅動能力較小,只適合部分電路設計。實現低功耗,主要是降低電源電壓,但是受亞閾值導通的特性影響,標準CMOS 工藝中的閾值電壓不會比深亞微米工藝的閾值電壓有較大的下降,因此電路工作電壓的降低將受到閾值電壓的限制。

采用襯底驅動是解決閾值電壓受限的重要途徑,根據漏電流公式:

看出當VDS為常數時,ID主要受VBS得控制,于是在襯底端加信號能有效地避開閾值電壓的限制,可以用非常小的信號加在襯底端和源端就可以用來調制漏電流,所以這種技術也可以用來實現低功耗。但是對于N(P)阱工藝,只能實現襯底驅動P(N)MOS管,嚴重限制了它的應用。

準浮柵技術由于與標準CMOS兼容并且性能優越,因此很多人預言,它將成為未來幾年低功耗模擬電路設計的新方向。

2. 浮柵和準浮柵技術

浮柵技術[5] 最開始是用于存儲器應用中,熟悉的EPROM,E^2PROM,FLASH 存儲器都廣泛地采用了浮柵技術。近年來,浮柵技術也被用于了模擬電路中。浮柵的工作原理是:一端與電氣連接,也就是我們傳統意義上的柵極,還有一個是沒有引外線的,它被完全包裹在一層SIO2 介質里面,是浮空的,所以稱為浮柵。

圖1 浮柵晶體管的結構及電氣符號

它是利用了浮柵上是否存儲電荷或存儲電荷的多少來改變MOS 管的閾值電壓,實際上是一個電壓加權處理的過程。浮柵晶體管的一個最顯著的特點是浮柵與其他端的電絕緣非常良好,在一般條件下,浮柵晶體管能將電荷保存達幾年之久,而損失的電荷量小于2%。通過改變浮柵電荷,改變其等效閾值電壓,從而實現所需要的功能。但由于它不能與標準CMOS工藝兼容,所以限制了它的應用。因此,Jaime Ramire-Angulo[1] 等人提出了基于浮柵技術的準浮柵技術。

準浮柵MOS管的結構同浮柵晶體管的結構類似,所不同的是他們的初始電荷方式不同,準浮柵NMOS(PMOS)晶體管是通過一個阻值非常大的上(下)拉電阻直接把浮柵接到電源VDD(GND)上,解決了它的初始問題。但是在集成電路工藝中,做一個阻值非常大的電阻是不太可能的,因為它電阻的值會隨諸多因素變化,精確它的值就不太可能,而且大阻值的電阻會占用大量的芯片面積,也是不經濟的。所以在COMS 工藝中可以用一個MOS管來代替電阻,將一個二極管連接的工作在截止區的MOS 晶體管來等效為一個阻值非常大的電阻。圖2 所示了一個兩輸入準浮柵NMOS 晶體管。

圖2 兩輸入準浮柵NMOS 晶體管

3 傳統的兩級運算放大器

運算放大器[2-3]是模擬集成電路和混合信號集成電路的基本電路單元,是模擬集成電路設計的關鍵模塊之一。它的性能對整個電路以及芯片的影響是至關重要的。

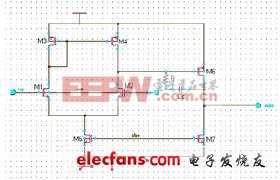

由于傳統的單級放大器不適合低壓設計,越來越多的設計使用多級放大器。與傳統的共源共柵結構相比,兩級運算能獲得更高的電壓增益和輸出擺幅。在本次的設計中,我們選用了圖3 所示的兩級運算結構。這種結構是目前應用得最為廣泛的電路之一,在低壓的工作環境下,它能得到較為理想的輸入共模范圍和輸出擺幅。并通過米勒補償電容和調零電阻串聯的補償電路使兩級運放的頻率響應特性和轉換速度得到了很好的改善,是一種簡單又比較有實際運用意義的電路。

對電路的結構分析,可以知道:

圖3 傳統的兩級運算放大器

為了實現低功耗設計,我們對以上傳統兩級運放采用準浮柵技術進行改進,因為準浮柵技術與標準的CMOS 工藝兼容,因此我們可以利用現有的工藝,對傳統的兩級運算放大器進行一些改進,就可以實現低功耗的設計,在目前是一種可以快速實現且低成本的方法。

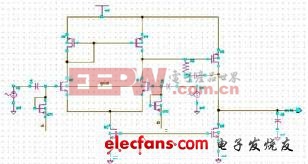

如圖4 所示為基于準浮柵技術的兩級運算放大器。為了滿足電源電壓下降的要求,我們采用準浮柵NMOS 差分對來代替傳統的差分對,對于相類似的器件尺寸和偏置電流,PMOS輸入差動對管比NMOS 輸入差動對管表現出較低的跨導。因此用NMOS 做為輸入對,可以比用PMOS 做為輸入對的兩級運算放大器[5] 得到更高的增益。

圖4 基于準浮柵技術的兩級運算放大器

輸入信號通過輸入耦合電容C 耦合到輸入管的柵極。將兩個輸入的NMOS 管的柵極偏置到VDD 上,因而兩個輸入管處于常導通的狀態,從而降低了對輸入信號的要求,即使輸入很低電壓,因為兩個輸入管的常導通狀態,電路也能正常工作,從而也降低了對電源電壓的要求,隨著電源電壓的下降,偏置電流也隨之降低,使電路能夠實現低功耗的要求。

采用準浮柵技術對電路進行改進后,由于該運放的輸入為交流耦合電路,因此可以濾掉由輸入電壓所帶來的直流失調。但是也從而也帶來了一個缺點,準浮柵運放只對交流信號進行放大,而不能作為直流比較器。且由于在輸入管引入了一個二級管連接的工作在截止區的MOS 管大電阻,因此可以判斷出主極點位于輸入管處,這樣的一個大電阻會引起單位增益帶寬的減小,但是它也會帶來更大的相位裕度,使系統更穩定。我們在選擇管子參數的時候,要考慮到它的具體應用環境,來決定它的性能指標。

準浮柵技術主要是實現低功耗問題,因此在設計中,運放的靜態功耗是一個非常重要的指標,在兩級運算放大器設計中,該電路的靜態功耗為

其中IM2為一級運放的偏置電流,IM6為二級運放的電流。可以看出為了減小運放的功耗,偏置電流應盡可能的小,但是隨著電流的減小又會帶來運放轉換速率的減小,這需要根據設計要求進行一個折中的考慮。

5 設計實現與仿真

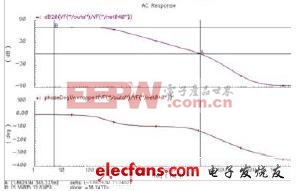

這次的設計中,我們采用了Chartered 0。35umCMOS 工藝,利用Spectre 對電路進行仿真分析[6] 。傳統放大器因為閾值電壓的影響,因此工作在± 2。5V 電壓下,而采用了準浮柵技術以后,可以使電路工作在1。2V 的低壓環境下,對運放做交流分析,表1 是傳統放大器與改進以后的放大器性能的比較,通過比較可以看出與我們前面分析的結果一致。根據仿真的幅頻和相頻特性,如圖5 所示,在保持增益,降低功耗的情況下,單位增益帶寬較小,但也可以滿足設計要求,相位裕度增加從而使系統穩定性增加。并由瞬態分析(如圖6),在降低電壓和電流的情況下,擺幅依然可以到達一個理想的值。仿真結構表明這樣的一個放大器可以適合在低壓低功耗的環境下應用。

表1 傳統放大器與改進以后的放大器性能的比較

圖5 幅頻和相頻特性

圖6 瞬態響應特性

電氣符號相關文章:電氣符號大全

晶體管相關文章:晶體管工作原理

電荷放大器相關文章:電荷放大器原理 晶體管相關文章:晶體管原理相關推薦

-

-

friends | 2013-09-29

-

-

-

TIfans | 2013-03-17

-

-

-

-

-

bjtiger | 2013-09-19

-

-

benny46 | 2013-06-20

-

-

-

-

-

renazan2000 | 2013-08-23

-

-

評論