可編程陣列邏輯(PAL)的輸出結(jié)構(gòu)及器件命名規(guī)則

1.PAL的輸出結(jié)構(gòu)

可編程陣列邏輯(PAL)是一種與項可編程、或項固定結(jié)構(gòu)的可編程結(jié)構(gòu),為能方便實現(xiàn)各種邏輯結(jié)構(gòu)功能,其輸出結(jié)構(gòu)通常有很多種結(jié)構(gòu),并且每種結(jié)構(gòu)有一類期間與之相對應(yīng)。下面是組合邏輯電路中常用的集中輸出結(jié)構(gòu):

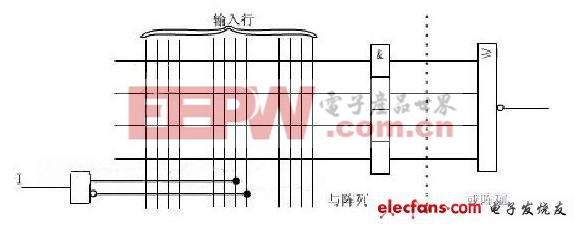

固定輸出結(jié)構(gòu)

固定輸出結(jié)構(gòu)是可編程器件中最簡單的輸出結(jié)構(gòu),其輸出就是或陣列的輸出,可以實現(xiàn)簡單的組合邏輯電路的功能,如下圖所示:

圖1 固定輸出結(jié)構(gòu)

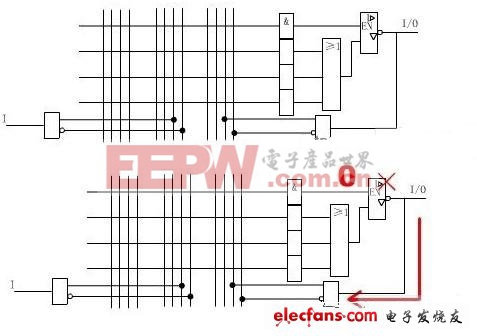

異步I/O輸出結(jié)構(gòu)

上面簡單的固定輸出結(jié)構(gòu)只能實現(xiàn)簡單的組合邏輯功能,如果希望實現(xiàn)其輸出端既可以當輸入端使用,又可以作為輸入端正使用,這是上面的電路就無法實現(xiàn)該功能,這就需要用到異步I/O輸出結(jié)構(gòu),如下圖所示:

圖2 異步I/O輸出結(jié)構(gòu)

從圖上可以看出當其中的三態(tài)門的使能端為0時,其三態(tài)門處理高阻狀態(tài),其內(nèi)部的輸出與I/O線隔離,這時I/O可作為輸入來使用;而當三態(tài)門的使用能端為1時,其I/O為輸出,這時內(nèi)部的邏輯功能不僅輸出端I/O端,還反饋到其內(nèi)部編程矩陣,這可以實現(xiàn)各種須帶反饋的電路,從而減少電路的外部連接,如在RS觸發(fā)器電路及各種帶級聯(lián)的電路。

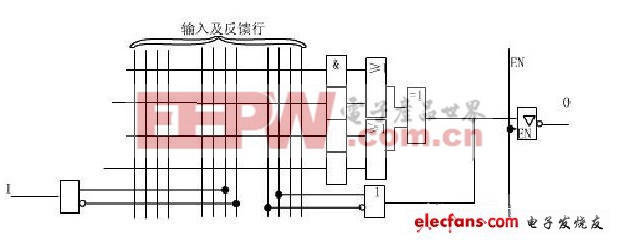

帶異或門的輸出

帶異或門的輸出端加上了一個異或門,這個異或門的加入使得電路的構(gòu)成發(fā)生了變化,如果一個邏輯函數(shù)需要的與項個數(shù)非常多(如一個四輸入的函數(shù),其與項的個數(shù)最多為16個),如果用反函數(shù)來實現(xiàn)時,發(fā)現(xiàn)其與項的個數(shù)較少(是16減去原函數(shù)的與項個數(shù)),異或門具有一個特點:當輸入端的一個輸入為0時,其輸出等于另一個輸入;而當輸入端中的一個固定為1時,其輸出為另一個輸入的非。這異或門的引入使得用原函數(shù)實現(xiàn)函數(shù)困難時可以通過反函數(shù)加以實現(xiàn)。

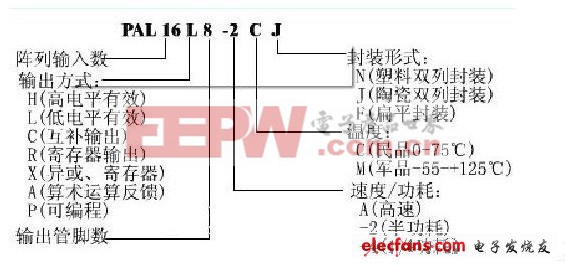

2.PAL器件的命名規(guī)則

PAL器件的命名與其輸入、輸出腳數(shù),輸出結(jié)構(gòu)有關(guān),下圖給出了其命名規(guī)則:

評論