淺談低電壓低靜態(tài)電流LDO的電路設(shè)計(jì)

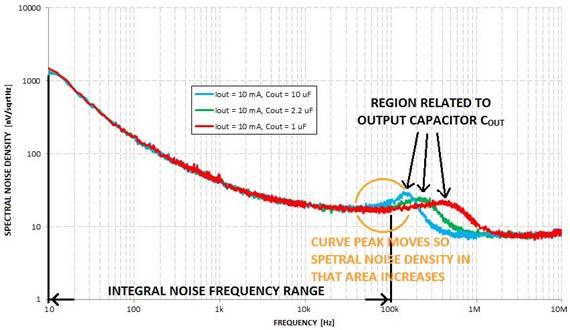

式中:ro1 和C1 分別是增益級(jí)輸出電阻和負(fù)載電容;ro2是緩沖級(jí)輸出電阻;Cpar 是功率管寄身電容;rop 是LDO輸出級(jí)的等效電阻;CL 為輸出負(fù)載補(bǔ)償電容。為了保證LDO有個(gè)良好的輸出暫態(tài)特性,CL 取值一般很大,因此極點(diǎn)p3 為L(zhǎng)DO環(huán)路的主極點(diǎn)。晶體管Q3集電極電流偏置為PTAT電流,因此增益級(jí)的輸出阻抗隨輸出負(fù)載電流和輸入電壓變化不大,同時(shí)增益級(jí)的負(fù)載電容主要由緩沖級(jí)輸入電容決定,所以極點(diǎn)p1 位置相對(duì)穩(wěn)定,故可以采用一個(gè)左半平面的零點(diǎn)補(bǔ)償。類(lèi)似如傳統(tǒng)LDO,本文采用一個(gè)電阻resr 與輸出補(bǔ)償電容串聯(lián)方式,獲得一個(gè)左半平面零點(diǎn):

基于上述分析,精簡(jiǎn)結(jié)構(gòu)LDO的開(kāi)環(huán)傳輸函數(shù)為:

式中 .其中:gmQ2 ,gmQ3 和gmp 分別代表晶體管Q2,Q3和功率管的跨導(dǎo);Rπ 3 是晶體管Q3的輸入電阻。當(dāng)p1 和z1 匹配比較精確,LDO環(huán)路只有兩個(gè)低頻極點(diǎn)p2 和p3 。因此,為了獲得60°的相位裕度,必須:

.其中:gmQ2 ,gmQ3 和gmp 分別代表晶體管Q2,Q3和功率管的跨導(dǎo);Rπ 3 是晶體管Q3的輸入電阻。當(dāng)p1 和z1 匹配比較精確,LDO環(huán)路只有兩個(gè)低頻極點(diǎn)p2 和p3 。因此,為了獲得60°的相位裕度,必須:

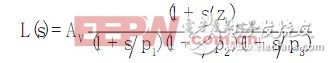

2 電路設(shè)計(jì)與實(shí)現(xiàn)

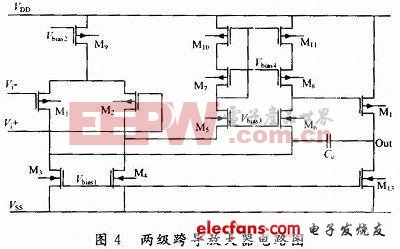

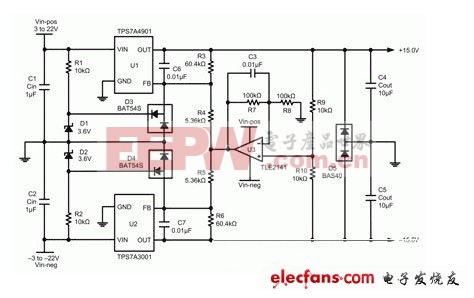

本文所提的低電壓、低靜態(tài)電流的精簡(jiǎn)結(jié)構(gòu)的LDO如圖2所示。LDO的輸出級(jí)是一個(gè)A類(lèi)共源級(jí)電路,包括PMOS功率管M1,三極管Q1、Q2,電阻R1,R2,R3,Resr和輸出負(fù)載補(bǔ)償電容C1.功率管M1有非常大的寬長(zhǎng)比來(lái)驅(qū)動(dòng)比較大的負(fù)載電流。因此M1的溝長(zhǎng)選取最小的值,達(dá)到盡可能小的寄身電容和尺寸面積。為了獲取好的暫態(tài)輸出特性以及環(huán)路穩(wěn)定,輸出補(bǔ)償電容取5 μF.帶隙基準(zhǔn)電路包括三極管Q1,Q2,Q3和電阻R1,R2,R3.選取Q2的射級(jí)面積為Q1和Q3的射級(jí)面積8倍,這是Q2面積和R2阻值折中結(jié)果。三極管Q3和晶體管M6構(gòu)成一個(gè)共集電極的電路,為環(huán)路提供高增益。緩沖級(jí)包括晶體管M2,M3和M4.因?yàn)镹MOS源跟隨器,在低負(fù)載情況下并不能完全關(guān)斷功率管,PMOS源跟隨器并不適合本電路的1.35低電壓環(huán)境,所以選用了二極管連結(jié)的PMOS負(fù)載共源級(jí)電路作為緩沖級(jí)。這種結(jié)構(gòu)不僅獲得低的輸出阻抗,同時(shí)達(dá)到180°的相位偏移,使整個(gè)閉環(huán)環(huán)路構(gòu)成一個(gè)負(fù)反饋。M3作用是在低負(fù)載電流的情況是為M4提供一些偏置電流,否則可能出現(xiàn)M4的柵源電壓過(guò)低,導(dǎo)致三極管Q3進(jìn)入飽和狀態(tài),降低Q3的電流增益,影響帶隙基準(zhǔn)電壓的精確度。通過(guò)Q4和M7構(gòu)成的偏置電路,使得三極管Q1,Q3有相等的集電極電流。晶體管M5,M8和M9構(gòu)成LDO的啟動(dòng)電路。在剛有電壓輸入情況下,M8和M9構(gòu)成一個(gè)反相器輸出一個(gè)低電壓信號(hào),使M5導(dǎo)通來(lái)啟動(dòng)整個(gè)電路。

3 電路仿真結(jié)果

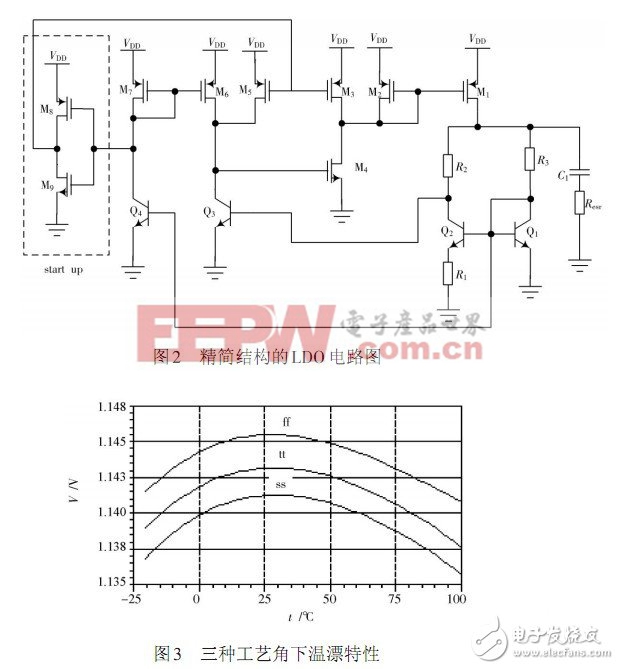

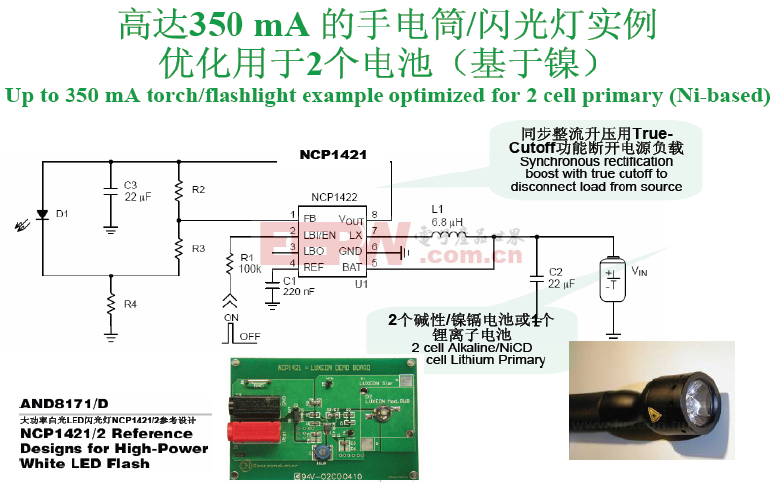

基于CSMC 0.5 μm 雙阱CMOS 工藝仿真模型,采用Cadence仿真軟件對(duì)精簡(jiǎn)結(jié)構(gòu)LDO進(jìn)行了三個(gè)工藝角(tt,ff,ss)下仿真驗(yàn)證。這個(gè)系統(tǒng)設(shè)計(jì)指標(biāo)的是讓LDO驅(qū)動(dòng)最大30 mA的負(fù)載電流,同時(shí)保持輸出電壓穩(wěn)定在1.14 V,輸入電壓最小為1.35 V.LDO 的溫漂曲線(xiàn)如圖3所示。

通過(guò)采用補(bǔ)償電容外接串聯(lián)電阻的方法,創(chuàng)造一個(gè)左半平面的零點(diǎn)來(lái)補(bǔ)償一個(gè)非主極點(diǎn),讓電路獲得比較好的環(huán)路相位裕度,在三個(gè)工藝角下,相位裕度都能達(dá)到70°(見(jiàn)圖4)。

評(píng)論