基于DSP的列車應變力測試系統設計方案

考慮到系統運行的環境比較惡劣,軌道線路的電磁干擾比較強,因此設計中要考慮信號完整性和電磁兼容性等問題。

表1總結了高速數字電路中常見的信號完整性問題與可能的原因和解決方法。

電源EMI是影響系統抗干擾能力的一個主要因素。簡單的方法是在每一個芯片的供電引腳上并聯一個電容進行電源濾波。影響系統抗干擾能力的另外一個因素是電路板上信號的走線質量,應盡量減少印制導線的電感量,導線盡量短而粗。同時要注意抑制印制板導線之間的串擾和避免高頻信號通過印制導線時產生的電磁輻射,此外,還要注意合理地安排電源地等。

結語

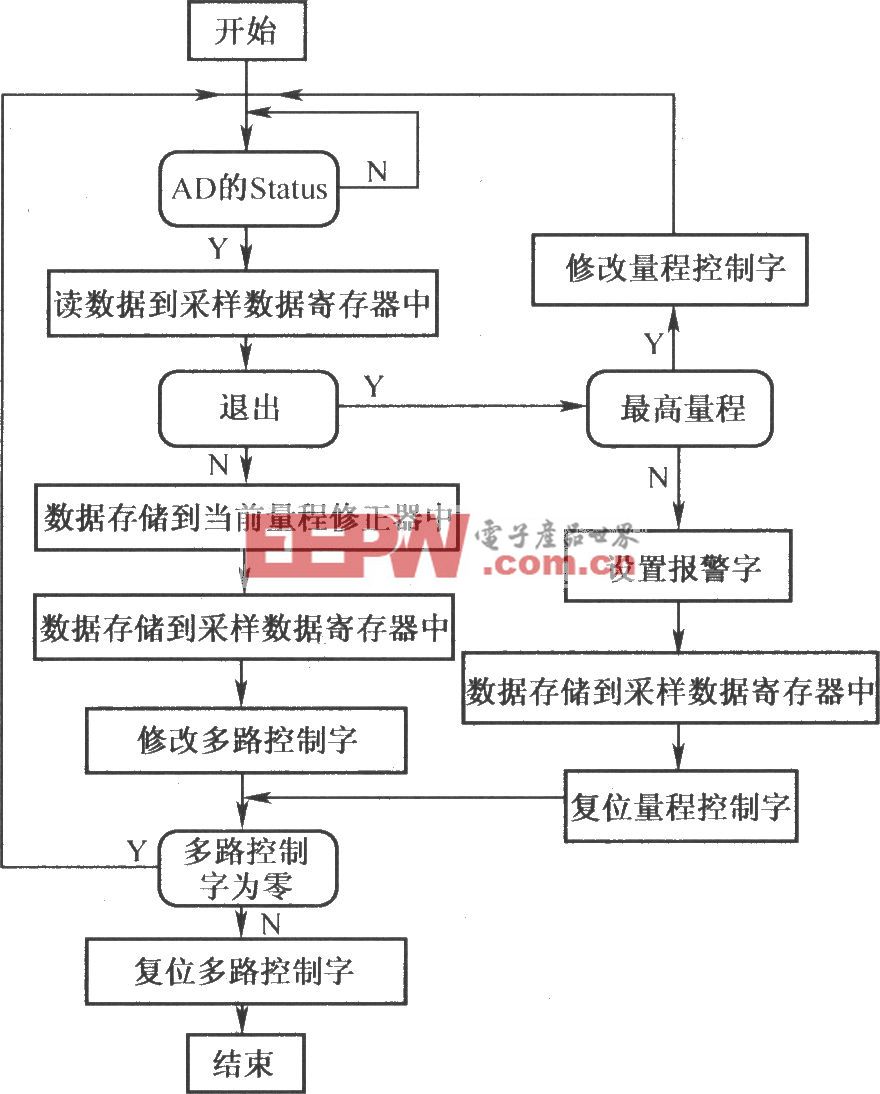

本文提出并設計的以DSP為核心的列車應變力測試系統,有效地解決了實際工程應用中的技術問題,并就測試系統的信號完整性分析和抗電磁干擾能力進行了考慮。從而為數據采集與處理領域提供了一個良好的參考方案

評論