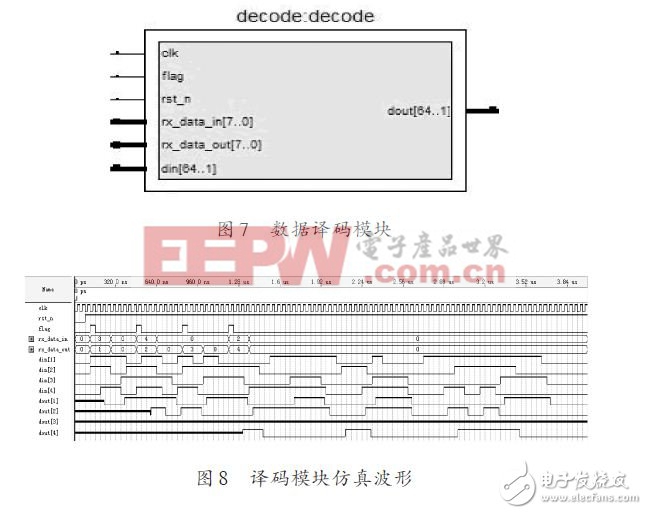

EXT-INDENT: 0px; MARGIN: 0px 0px 20px; PADDING-LEFT: 0px; PADDING-RIGHT: 0px; FONT: 14px/25px 宋體, arial; WHITE-SPACE: normal; ORPHANS: 2; LETTER-SPACING: normal; COLOR: rgb(0,0,0); WORD-SPACING: 0px; PADDING-TOP: 0px; -webkit-text-size-adjust: auto; -webkit-text-stroke-width: 0px"> 由于64×64的仿真很繁瑣且不易操作,所以對4×4的譯碼模塊進行仿真,仿真結(jié)果如圖8所示,輸出1與輸入3相連,輸出2與輸入4相連,輸出3懸空,輸出4與輸入2相連。

4 結(jié)語

本文采用FPGA作為實現(xiàn)控制邏輯的核心部件,提出了基于FPGA的基帶64×64 數(shù)據(jù)分配矩陣設(shè)計方案,并介紹了上位機的軟件設(shè)計思路和FPGA的內(nèi)部編程實現(xiàn)及仿真。經(jīng)驗證本系統(tǒng)基本能實現(xiàn)基帶數(shù)字信號的分配路由,從而證實了該方案具有規(guī)模大、成本低、高速等特點,可廣泛應(yīng)用于大規(guī)模基帶數(shù)字系統(tǒng)測試及信號程控分配調(diào)度中。

評論