SPI4.2總線應用和調試

圖3 日歷長度和重復次數都為4的數據傳輸示意圖

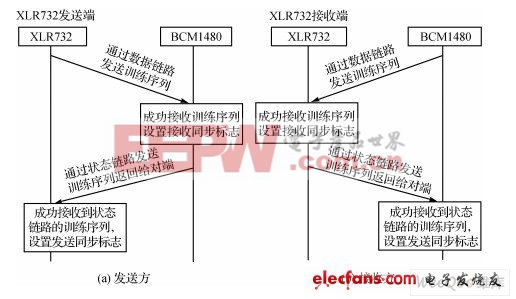

圖4 收發同步過程示意圖

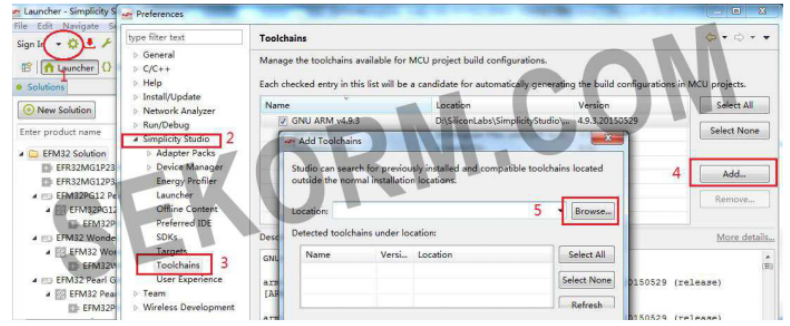

SPI4.2總線接口的調試包括兩個重要步驟:鏈路的同步和數據的正常收發。

在調試鏈路同步時,首先必須查看總線兩端的初始化參數配置。因為SPI4.2 總線協議是一個對等端數據傳輸協議,所以大部分參數需要雙方的匹配和協商,特別是接收方和發送方的CALENDAR_LEN和CALENDAR_M參數。

如何查看同步呢?芯片通常會提供一個狀態寄存器來反映總線的同步。“接收同步標志”只能說明在數據鏈路上成功接收到對端的訓練序列,但不能保證接收的狀態鏈路是正常的,如果需要確認可查看對端的“發送同步標志”。在收發雙向通道應用中,只有兩端的“接收同步標志”和“發送同步標志”都置位了,總線才算同步。此時,可以確認總線兩端的物理連接是正確的,握手成功。

如果不能同步,就必須檢查兩端的“接收同步標志”和“發送同步標志”,判斷是哪一端出了問題。檢查是否有DIP4和DIP2錯誤,如果有此類錯誤,說明鏈路上信號質量可能不佳,可以用示波器測量信號波形。如果信號質量確實不好,可以通過提高信號驅動能力或者調整硬件匹配阻抗來優化。

如果兩端的接收和發送都沒有同步,就必須測量芯片的電壓、工作頻率、重啟等信號。如果兩端的“接收同步標志”和“發送同步標志”都已經置位,說明雙方的接收和發送都同步,可以正常收發數據了。在大流量數據傳輸過程中,最相關的是FIFO隊列的參數配置,配置不當會導致錯包或丟包。以NetLogic公司的XLR732網絡處理器為例[2],SPI4.2總線的發送模塊的所有邏輯端口共享一個FIFO隊列,寬度為16字節,長度為128;接收模塊的所有邏輯端口共享一個FIFO隊列,寬度為16字節,長度為512。每個邏輯端口所占用的隊列地址和大小都可以通過寄存器配置。

假如某個端口接收端隊列的長度是48,MaxBurst1是12,MaxBurst2是8。那么當該模塊接收數據時,如果由于某些原因(例如軟件來不及處理),接收隊列只剩下12個空位,也就是接收隊列已經有48-12=36個空位被占用時,它將通過狀態鏈路向對端發送“餓”的狀態信號(反壓信號)。對端收到該信號后實施流控策略,根據本端發送端的MaxBurst1設置值發送數據,該值表示接收到“餓”狀態信號后最多還可以發送的數據塊數目。所以接收端的MaxBurst1 的值一定要大于對端發送端的Max

評論