IDT70V9289型高速同步雙口SRAM的原理及應用

關鍵詞:SRAM 同步 流通模式 流水線模式

1 引言

隨著科技的發展和高速設備的不斷涌現,數據傳輸率也越來越高。而由于傳輸方式的不同,各種高速設備在連接時能否實現可靠的數據交換就顯得十分重要。高速雙口SRAM的出現為解決這一問題提供了一種有效途徑。IDT70V9289是IDT公司新推出的高速同步雙口靜態存儲器,其容量為64k16bit,具有設計簡單,應用靈活等特點。

2 IDT70V9289的結構及功能

2.1 內部結構

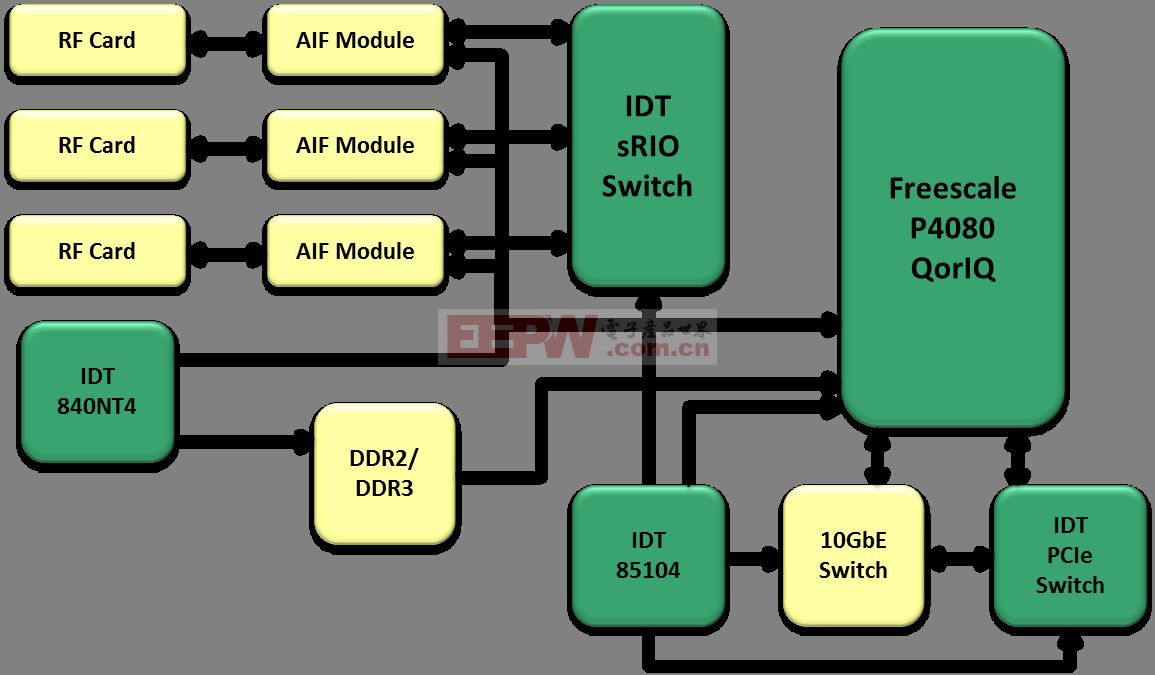

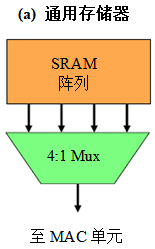

圖1示出IDT70V9289的結構框圖,它主要由I/O控制器、存儲器陣列、計數器/地址寄存器和一些邏輯電路組成。

圖1

2.2 功能特點

真正的雙端口存儲器,完全同步操作

3.5ns時鐘建立時間,0ns保持時間(所有控制、數據和地址輸入)

具有數據輸入、地址和控制寄存器

存儲容量達1024kbit(64k16bit);

高速數據存取,其TCD(時鐘上升沿與數據輸入/輸出的時延)為

商業級:6/7.5/9/12ns(最大)

工業級:9ns(最大)

應用IDT公司的高性能CMOS技術,所耗低

工作時:500mW(典型值)

待機時:1.5mw(典型值)

計數使能和重置功能

通過FT/PIPE引腳選擇任意端口的流通(folw-through)或流水線輸出模式

可對多路傳輸總線中的獨立高位字節和低位字節進行控制

LVTTL接口電平,3.3V(0.3V)單電源供電

2.3 引腳功能(以左邊端口引腳為例)

VDD:電源輸入端,起濾波作用的旁路電容器應盡可能靠近電源引腳,并直接連接到地;

VSS:接地引腳;

CE0L,CE1L:使能端,當CE0L為低電平且CE1L為高電平時,電路工作。該引腳可允許每個端口的片上電路進入低功耗的待機模式;

R/WL:讀/寫使能,此端為高電平時讀出,為低電平時寫入;

OEL:異步輸出使能;

A0L-A15L:地址同步輸入端;

I/O0L-I/O15L:數據輸入/輸出端;

CLK::存儲器工作時鐘,所以輸入信號在該時鐘上升沿有效;

UBL:高位字節選擇,低電平有效;

LBL:低位字節選擇,低電平有效;

CNTENL:計數器使能,當時鐘上升沿到來時,如果該引腳為低電平,則地址計數器工作,優先級高于其它引腳;

CNTRSTL:計數器重置,低電平有效,優先級高于其他引腳;

FT/PIPEL:流通(flow-through)和流水線模式選擇,高電平有時為流水線模式,此時輸出有效發生在CE0L為低電平且CE1L為高電平的二個周期。

ADSL:地址選通使能,低電平有效,優先級高于其他引腳。

3 應用舉例

以IDT70V9289為核心,配以適當的控制信號,即可使不同傳輸方式的雙路高速數據流實現無損傳輸。下面以某高速誤碼儀與CY7C68013型高速USB單片機的連接為例,介紹IDT70V9289的應用及應注意的問題。

3.1 讀模式選擇

在設計中,高速誤碼儀的Virtex_II XC2V250與CY7C68013進行數據交換,由于CY7C68013采用突發方式傳輸且傳輸速度高達300Mbit/s,而Virtex-II XC2V250只能檢測連續數據流的誤碼,因此正好可以應用IDT70V9289實現高速數據流的無損傳輸。IDT70V9289提供二種讀數據模式(流通模式和流水線模式)。為了實現高速傳輸和降低時序設計的復雜度,設計選擇了流水線模式。下面簡述二種模式的區別。

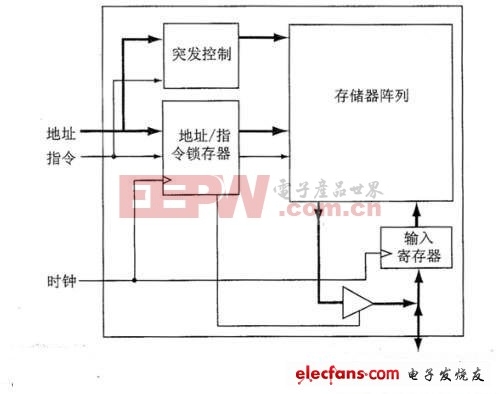

(1)結構差別

二者在寫入過程中完全一樣,都是通過輸入寄存器緩沖數據,但在讀出過程中,流水線模式通過輸出寄存器緩沖數據而流通模式則沒有。如圖2所示,在流水線模式中輸入寄存器和輸出寄存器工作在同一時鐘邊沿。

(2)時序差別

結構差別反映在時序關系上就是流通模式的數據輸出比流水線模式提前一周期,并與存儲器陣列的讀數據同在一個時鐘周期,并與存儲器陣列的讀數據同在一個時鐘周期,如圖3所示,這樣,可以實現地址輸入和數據輸出的同步,從而滿足一些電路的時序要求;而流水線模式由于有輸出寄存器,其輸出引腳上的讀數據在幾乎整個時鐘周期內都是可用的,因而為器件取數據提供最佳的建立時間,并允許在更高的時鐘頻率下進行操作,同時設計者也無需擔心電路設計技巧和定時通路。更要注意的是:由于存在這種時序差別,設計者在選擇讀模式時,要考慮到相應的時序變化,以免造成讀取數據錯誤。

3.2 電路設計

由于本設計的數據傳輸率高達300Mbit/s,而IDT70V9289的容量僅有1024kbit,所以必須采取邊讀邊寫的方式緩沖數據。但是,IDT70V9289并不允許雙端口對同一地址同時進行讀和寫,也沒有像以前的SRAM(如IDT7024)那樣設計操作忙邏輯,而是制定了一套讀寫規則。由于這套讀寫規則比較復雜,為了降低時序關系的復雜度,本設計將IDT70V9289分成容量相等的二個區域,把地址預存入Virtex-II XC2V250和CY7C68013的RAM中。

當Virtex-II XC2V250向CY7C68013傳輸數據時,也可以通過片選端啟動CY7C68013和IDT70D9289,其余過程與上面所述類似,不過由于CY7C68013有內置時鐘,為了保持時間一致,此時的時鐘仍由CY7C68013提供。

評論