PLD設計方法及步驟

在項目管理器下,選擇左邊方框中對應于源文件的文件名,雙擊右邊區域中的Reduce Logic可以看到如上圖所示的編譯過程,如源文件無誤,則編譯器最終給出編譯報告,說明完成該邏輯所需要的資源及經化簡后的邏輯表達式;如源文件存在問題問題,則編譯器會說明錯誤的原因及地方。

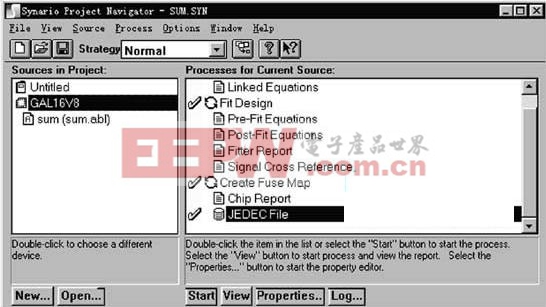

(6)熔斷絲文件形成

在項目管理器左邊的區域選擇使用的器件(GAL16V8),雙擊右邊區域中的Create Fuse Map, 可看到如下圖所示的熔斷絲文件的形成過程,如報設計的邏輯報需要的資源GAL16V8可以實現的話,將最終形成擴展名為.JED的熔斷絲文件。

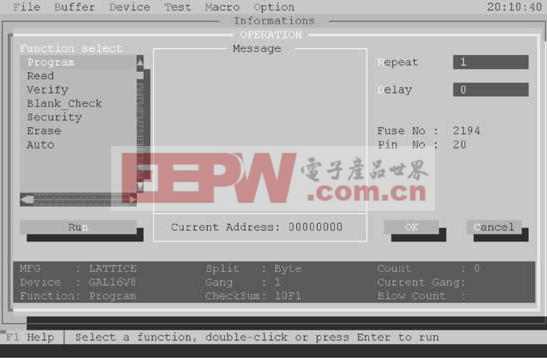

(7)程序下載

JED的文件須下載到具有的GAL器件中,才能完成其最終的設計,下載JED文件到GAL須用專門的硬件設計,這種專門的的設備即通常講的編程器。這種設備與計算機的并口或串口相連,通過相應軟件將JED文件下載到GAL器件中到。如下圖給出了Super編程器下載JED文件的畫面。

在利用編程器進行下載時,首先選擇器件的廠家,不同的廠家器件特性有所不同,故應選擇對應的生產廠家,其次選擇器件的型號,這時可以將需要下載的JED文件讀入緩沖區,最后對器件進行編程,編程器將JED文件下載后還自動進行一次校驗,如器件工作正常,則編程 器軟件可告知下載正常,否則說明器件損壞。

由于GAL器件是使用CMOS工藝生產的器件,故在對GAL器件編程時應注意計算機及編程器的接地是否良好,工作人員的人體是否帶靜電。

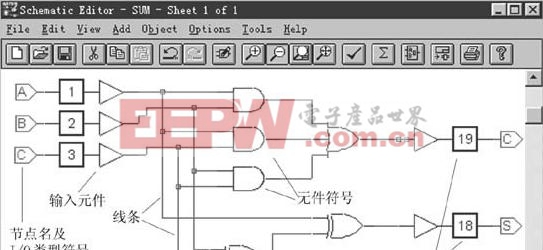

2.原理圖輸入設計法

原理圖輸入法的使用前面步驟與ABEL語言設計的前兩步相同,下面是原理圖設計的步驟:

(1)選擇源文件類型中選擇Schematic,輸入對應的圖形文件名后將出現下圖所示的原理圖輸入界面。

(2)添加元件:選擇菜Add中的Symbol命令,屏幕出現Symbol Libraries對話框,選擇需要的件,其中: GATE:邏輯門電路;ARITHS:數學運算元件;IOPAD:輸入輸出元件;MUXEX:多路選擇開關 ;REGS:寄存器。

(3)連接兩元件:從Add菜單中選擇Wire,用MOUSE左鍵在須連接處單擊后,拖動MOUSE到另一點再單擊就將兩點連接上了。

(4)在輸入輸出端連上輸入/輸出元件:在菜單Add上選擇Symbol中的IOPAD元件,在電路的輸入/輸出畫上IOPAD元件。

(5)給接口輸出端賦名:從Add菜單中選擇Net Name項,從屏幕底部輸入欄中輸入網絡名并按回車,網絡名會粘在光標上隨MOUSE一起移動,將光標移到輸入或輸出端單擊,網絡名就被 放置在輸入/輸出處。

(6)給接口的輸入輸出端標注類型:在Add菜單中選擇I/O Markers,輸對應的輸入輸出標上輸入與輸出的標記。

(7)給器件鎖定管腳:從Add中選擇Symbol Attribute將MOUSE光標移到輸入輸出端的IOPAD上單擊,將SynarioPin=*中的*改為所須的輸出管腳號。

到此一個完整的原理圖已經輸入完畢,將電路圖保存后退出后就可以與ABEL_HDL語言一樣進行編譯,最終開成JED文件。

ABEL-HDL基本算術運算符號

(1)基本的運算表示

ABEL-HDL語言運算可分為邏輯運算和算術運算。下面兩個表格分別列出了兩種運算的符號及功能,下面表格中紅底的項為時序電路中才會使用到。

ABEL-HDL基本邏輯運算符號

運算符 | 優先級 | 功能 | 例子 | 含義 |

! | 1 | 取反 | !(AB) | (AB)的非 |

2 | 與運算 | AB | A·B | |

# | 3 | 或運算 | A#B | A+B |

$ | 4 | 異或運算 | A$B | A⊕B |

= | 賦值 | A=5 | 將5賦給A | |

== | 數值相等 | A==1 | 用于判斷數值相等 | |

!= | 數值不等 | A!=1 | 用于判斷數值不等 |

ABEL-HDL基本算術運算符號

運算符 | 功能 | 舉例 | 含義 |

+ | 算術加 | C=A+B | 將A與B相加,將積再賦給C |

- | 算術減 | ||

* | 算術乘 | ||

/ | 算術除 | ||

,>> | 左,右移位 | AB | 將A左移B位 |

(2)關鍵字

關鍵字 | 作 用 | 舉 例 |

module | 說明模塊的開始,與END對應 | MODULE tran |

End | 模塊的結束 | END |

Title | 說明模塊的名稱(可省略) | Title 'U2 is a decode' |

Equations | 表明與器件相關的方程式的開始 | |

Pin | 說明器件I/O的引腳 | CLK,A Pin 1,2; |

Istype | 說明輸出信號的屬性 | A Pin 19 istype 'COM'; |

Test_vectors | 測試向量的開始 | |

Truth_table | 真值表的開始 | |

When then Else | 當什么時就怎樣,否則怎樣 | When b then c=0 esle a=b |

If then else |

3)ABEL語言設計舉例

例 寫出全加器的ABEL-HDL語言的源文件。

分析:在組合邏輯電路中我們分析了全加器的電路,我們可以用真值表、邏輯表達式、電路圖等幾種方式來描述其邏輯功能。其表達式寫為:

其值表可寫為:

Ci | A | B | Co | S |

0 | 0 | 0 | 0 | 0 |

0 | 0 | 1 | 0 | 1 |

0 | 1 | 0 | 0 | 1 |

0 | 1 | 1 | 1 | 0 |

1 | 0 | 0 | 0 | 1 |

1 | 0 | 1 | 1 | 0 |

1 | 1 | 0 | 1 | 0 |

1 | 1 | 1 | 1 | 1 |

該邏輯用真值表和表達式皆可以表示,即ABEL的源文件可以有兩種表達方式。

源文件1:用表達式來表示

源文件 | 說 明 |

Module FSUM; | 模塊定義,FSUM為模塊名,每行結束用分號結束 |

A,B,Ci pin 1,2,3; | 定義A,B,Ci對應管腳1,2,3 |

S,Co pin 19,18 istype 'com'; | 定義S,Co的管腳,并定義其為組合邏輯電路輸出 |

Equations | 表示下面一段為邏輯表達式 |

S=A$B$Ci; | |

Co=AB+ACi+BCi; | |

Test_vectors ([Ci,A,B]->[Co,S]) | 測試向量定義,下面為測試向量用于模擬邏輯功能 |

[0,0,0]->[0,0]; | |

[0,0,1]->[0,1]; | |

[0,1,0]->[0,1]; | |

[0,1,1]->[1,0]; | |

[1,0,0]->[0,1]; | |

[1,0,1]->[1,0]; | |

[1,1,0]->[1,0]; | |

[1,1,1]->[1,1]; | |

End | 模塊結束 |

評論