提高數字設計寄生提取的精度

寄生參數提取在集成電路 (IC) 設計中是必不可少的,因為它可以識別可能影響電路性能的意外電阻、電容和電感。這些寄生元件來自電路的布局和互連,會影響信號完整性、功耗和時序。隨著 IC 設計縮小到更小的節點,寄生效應變得更加明顯,因此精確提取對于確保設計可靠性至關重要。通過對這些效應進行建模,設計人員可以調整電路以保持性能,避免信號延遲或功率損耗等問題,并成功實現設計收斂。

什么是寄生參數提取

在半導體設計中,寄生元件(如電阻、電容和電感)是集成電路 (IC) 物理制造過程中意外但不可避免的元件。這些元素是所用材料和制造過程復雜性的結果。雖然寄生元件不是原始設計的一部分,但它會顯著影響電路性能。例如,寄生電阻會導致電壓降和功率耗散增加,而寄生電容會導致相鄰導線之間的信號延遲、失真和串擾。此外,interconnect parasitic 會引入傳播延遲,從而影響 timing 和信號完整性,從而導致更高的功耗和更低的整體性能。

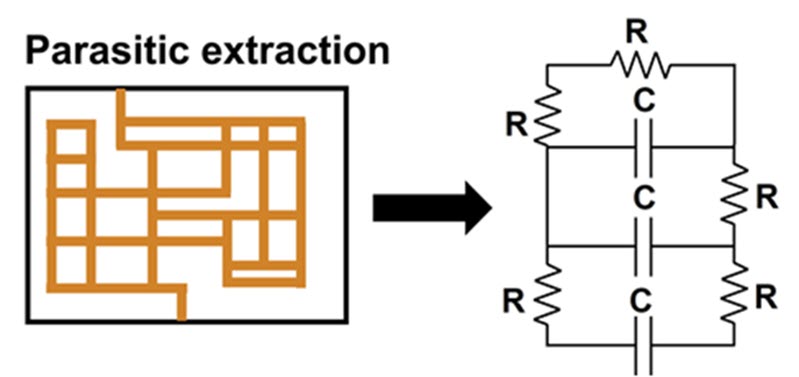

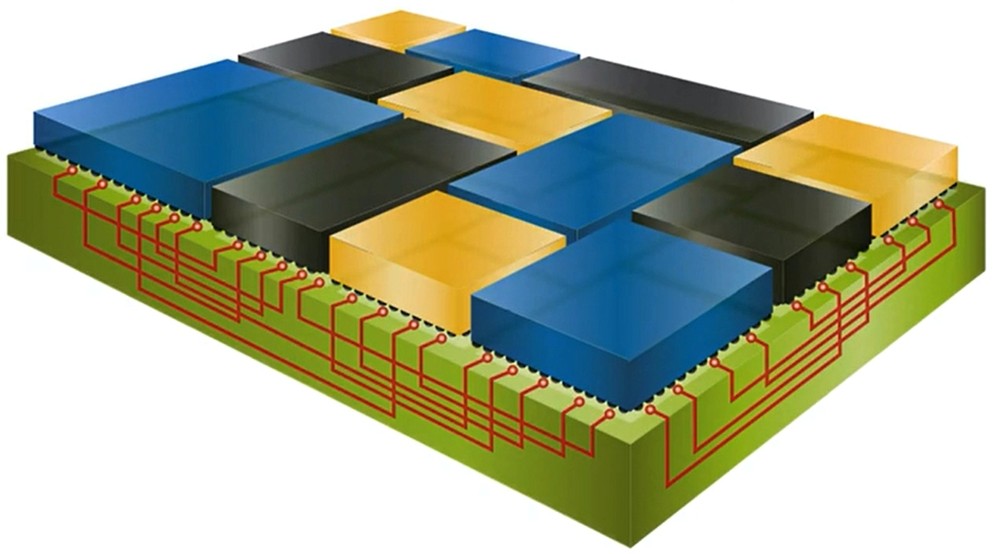

寄生參數提取是 IC 設計中的一個關鍵過程,用于識別和模擬這些意外的寄生效應,以確保可靠的性能。在數字設計中,寄生參數提取在很大程度上依賴于 LEF (Library Exchange Format) 和 DEF (Design Exchange Format) 等標準化格式,它們描述了設計的邏輯和物理方面(圖 1)。

圖 1.寄生參數是從有關設計的物理和邏輯信息中提取的。

寄生參數提取過程通常遵循以下關鍵步驟:

數據準備:此步驟涉及組裝和對齊邏輯和物理設計數據,通常來自 LEF 和 DEF 文件。目的是確保每個 logical component 都正確映射到 layout中的相應物理位置,確保寄生 extraction 過程的準確連接。

提取:在提取過程中,從設計布局和技術數據中識別和捕獲寄生元件,例如電阻、電容和互連。這構成了理解這些寄生元件如何影響電路整體性能的基礎。

歸約:提取寄生元后,使用分布式 RC 或集總元模型等模型對其進行簡化。這些模型壓縮了寄生數據,使其更易于管理,同時仍能準確反映寄生效應以進行仿真和分析。

驗證:提取后,對數據進行驗證。這包括將寄生參數數據與設計規范和仿真結果進行比較,以確保其符合預期的電路性能,并符合必要的設計規則和簽核標準。

優化:驗證寄生效應后,設計人員可以應用各種優化技術來減少它們對電路的負面影響。這可能包括優化 routing paths、添加 buffers 或進行其他調整,以提高性能、時序、功耗和信號完整性。

準確的寄生參數提取對于成功的 IC 設計至關重要,尤其是在技術進步和寄生效應變得更加明顯的情況下。通過系統地建模、驗證和優化這些效應,設計人員可以確保他們的電路在制造和最終生產期間可靠運行并滿足所需的規格。

模擬和數字設計流程

模擬和數字設計流程是半導體設計中的兩種不同方法,每種方法都適合模擬和數字集成電路 (IC) 的特定要求。模擬設計涉及處理連續信號的電路,例如放大器、濾波器和模數轉換器 (ADC)。在這些電路中,精度對于降低噪聲、失真和功耗至關重要。設計人員面臨的挑戰包括平衡電源效率和降噪之間的權衡,需要手動調整布局以避免因微小變化而導致的性能問題。SPICE 仿真器等工具有助于對不同條件下的電路行為進行建模,以確保可靠性和性能。模擬電路對其物理布局高度敏感,并在不同的工作條件下進行了全面測試。

另一方面,數字設計側重于使用二進制信號(0 和 1)的電路和組件,例如邏輯門、觸發器和各種類型的邏輯電路。數字設計優先考慮速度、能源效率和抗噪性,更多地依賴自動化和標準化組件來簡化流程。Verilog 和 VHDL 等工具允許設計人員定義電路的行為,然后將其自動綜合到布局中。數字工作流程利用時序分析、邏輯仿真和驗證工具來確保電路正常運行并滿足性能要求。雖然數字電路可能很復雜,但與模擬電路相比,它們的二進制特性允許更直接的布局。

然而,隨著技術的進步和節點規模的縮小,模擬和數字設計都面臨著新的挑戰。模擬設計必須處理增加的噪聲靈敏度和寄生效應,而數字設計需要解決更高電路密度下的時序、功耗和信號完整性問題。盡管存在這些復雜性,但現代設計工具和方法有助于確保 IC 滿足所需的性能、功耗和可靠性標準。這兩種設計流程在 IC 開發中都發揮著關鍵的互補作用,模擬設計側重于精度和手動調整,而數字設計則強調自動化和效率。這兩個領域的設計人員都必須在快速發展的技術環境中進行復雜的權衡,以生產高性能、可靠的 IC。

寄生提取工具

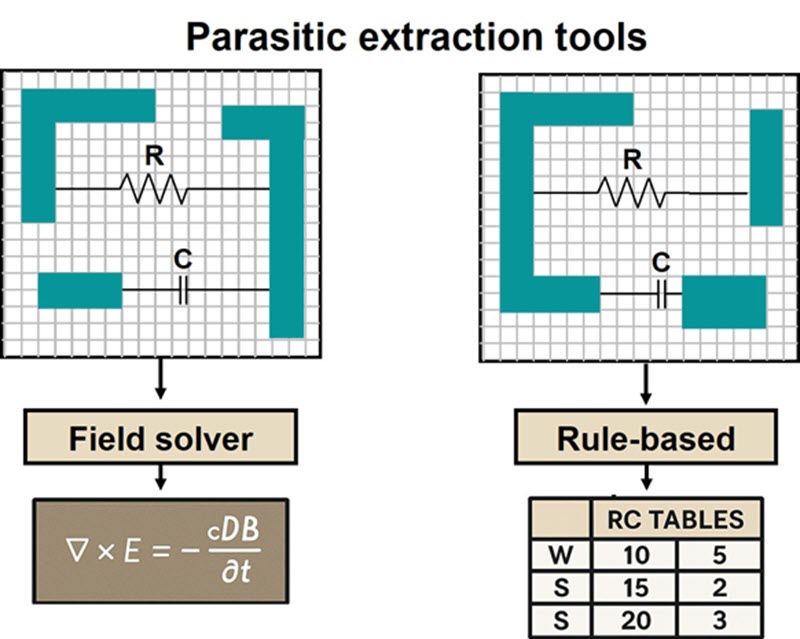

用于半導體設計的寄生提取工具通常分為三大類:基于場求解器、基于規則的提取和模式匹配,每種工具都有自己的優勢,適合不同的設計要求(圖 2)。

圖 2.用于寄生提取的軟件工具傳統上是場求解器或基于規則的工具。模式匹配是一種較新的技術。

場求解器。基于場求解器的方法使用數值技術來求解電磁場方程,例如麥克斯韋方程組,這使它們能夠高精度地對復雜的幾何形狀和互連進行建模。這些方法在捕獲分布式寄生方面表現出色,這使得它們對于對電磁現象的詳細洞察至關重要的設計特別有用。這種精度對于高頻電路、射頻 (RF) 設計和其他需要深入了解寄生效應以確保性能完整性的高級應用至關重要。然而,場求解器方法的權衡是它們的計算強度。由于它們求解跨精細幾何細節的復雜數學方程,因此需要大量的計算資源和時間,尤其是在應用于大規模設計時。這限制了它們在日常工作流程中的廣泛使用,使它們主要用于需要最高準確性的專業任務。

基于規則。相比之下,基于規則的提取工具根據預定義的模型和設計指南進行作,這使它們能夠以更快、更可擴展的方式估計寄生元素。這些工具依賴于從以前的模擬和物理定律中得出的既定規則,將它們應用于整個設計布局以提取寄生效應。盡管基于規則的方法可能無法捕獲與現場求解器相同水平的精細細節,但它們效率很高,可提供更快的提取時間,并且能夠處理更大、更復雜的設計,而不會占用大量計算資源。這使它們成為大多數數字和模擬 IC 設計工作流程的首選,在這些工作流程中,設計人員優先考慮速度、精度和可擴展性之間的平衡。基于規則的工具特別適合主流應用,在這些應用中,精度的權衡是可以接受的,并且設計幾何形狀不像高頻或射頻電路那樣復雜或要求苛刻。這些工具也更加用戶友好,需要更少的設置和計算開銷,使它們可用于更廣泛的設計項目。

模式匹配通常被認為是一種 2.5D 提取技術,通過識別設計中重復出現的布局模式來提供幫助。它使用特定幾何配置的預先表征寄生值來加快提取過程,而無需對每個實例執行復雜的計算。圖案匹配提供了速度和精度之間的平衡,使其適用于涉及重復結構的大規模設計,例如標準單元或重復電路塊。

選擇提取工具

不同寄生提取工具之間的決定取決于設計的具體需求。場求解器方法非常適合精度不影響的特殊應用,例如射頻、微波和毫米波設計,或具有密集和復雜互連結構的高級節點。基于規則的工具是主流設計流程的支柱,為大多數數字和模擬 IC 提供實用且可擴展的解決方案。圖案匹配提供了靈活的中間解決方案,提高了重復結構的提取效率。

設計人員必須評估其設計的性能、資源限制和復雜性,以選擇適當的方法。在許多情況下,可以使用不同方法的組合:用于需要高精度的關鍵區域的現場求解器和基于規則的方法用于大部分設計,在整個設計過程中提供效率和準確性的最佳平衡,以及模式匹配以優化重復設計模式的效率。

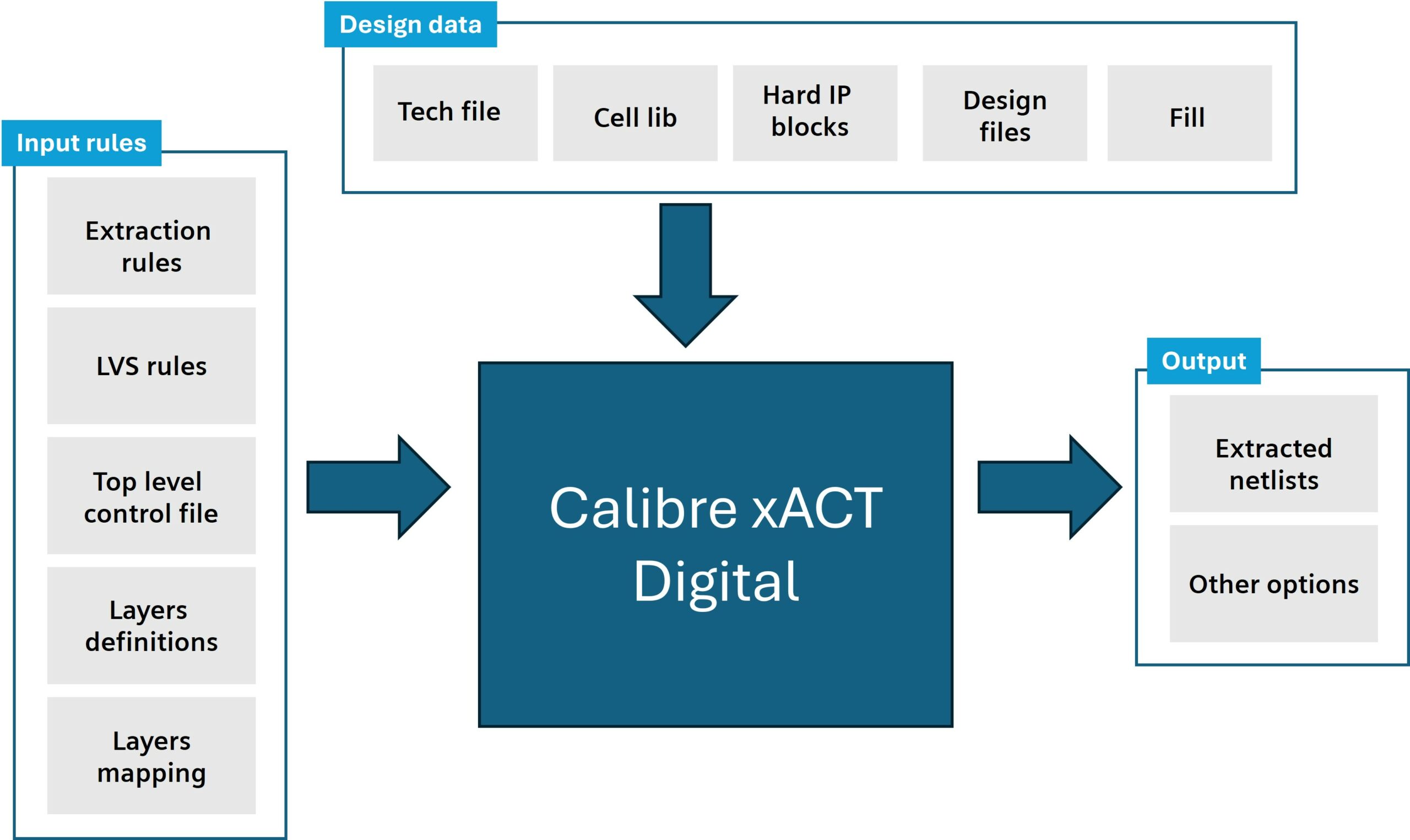

有一些工具,包括 Calibre xACT,它采用基于規則和場求解器的方法,并提供模式匹配。對于大多數設計人員來說,擁有一種高精度的工具來提取互連寄生效應(如電阻和電容)對于了解IC性能至關重要。先進的提取工具可以捕獲 IC 內互連和器件之間的詳細交互,為優化設計性能和解決信號完整性挑戰提供重要見解(圖 3)。

圖 3.數字提取流的輸入和輸出。

圖 3.數字提取流的輸入和輸出。

結論

高效的寄生提取對于通過精確建模電阻、電容和其他寄生元件來優化 IC 性能至關重要。設計人員在提取工具方面有多種選擇,因此應考慮支持模擬和數字設計流程、能夠發現并減輕影響信號完整性、時序收斂和電源效率的寄生效應,并且適用于所有設計節點的工具。精確的提取結果可幫助設計人員在設計過程的早期做出明智的決策,確保穩健可靠的 IC 開發。

評論